**Ninevah University**

**College of Electronics**

**Communication Dept.**

# Digital Technique

Digital Technique is a subject that helps you to understand binary numbers and give the students good information about the most famous digital circuits that were used in every digital system

2021-2022

## **Digital Technique**

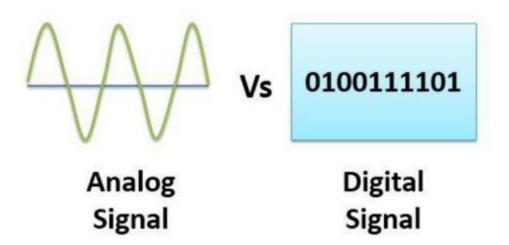

Analog and digital signals : They used to transmit information, usually through electric signals. In both these technologies, the information, such as any audio or video, is transformed into electric signals. The difference between analog and digital technologies is that in analog technology, information is translated into electric pulses of varying amplitude. In digital technology, translation of information is into binary format (zero or one) where each bit is representative of two distinct amplitudes.

The analog signal is a varied its amplitude with the time such as 0 volt to 40 volt linearly, while the digital signal has two values of amplitude 0 volt and 5 volt.

As this subject is concerned with digital so we need first of all to know what the binary number system is.

How could you understand how binary number system works? Let us start with decimal which consists of 10 symbols 0, 1, 2.....9 So when we need to write number ten there is no symbol for it. We put the zero symbol in the first digit and put the smallest symbol that is (1) in the second digit like this

10

After that we will increase the zero to 1, 2, up to 19 after that again we will put zero in this digit but increase the second digit up to 1 and so on...

Now look at the table 1

| النظام العشري Decimal | النظام الثنائيBinary |

|-----------------------|----------------------|

| 0                     | 0                    |

| 1                     | 1                    |

| 2                     | 10                   |

| 3                     | 11                   |

| 4                     | 100                  |

| 5                     | 101                  |

| 6                     | 110                  |

| 7                     | 111                  |

| 8                     | 1000                 |

| 9                     | 1001                 |

| 10                    | 1010                 |

| 11                    | 1011                 |

| 12                    | 1100                 |

| 13                    | 1101                 |

| 14                    | 1110                 |

| 15                    | 1111                 |

| 16                    | 10000                |

| 17                    | 10001                |

In binary number system we have only two digit 0 and 1

Let us count as before

| Zero | yes we have this symbol | 0 |

|------|-------------------------|---|

| One  | yes we have this symbol | 1 |

Two the symbol are finished! What we will do as I do with decimal number I will put a zero symbol in the first digit and put 1 in the second digit

| Two    | yes we will use two symbols      | 10 |

|--------|----------------------------------|----|

| Thomas | in any sea the 1st digit has any | 11 |

| Three | increase | the | 150 | digit | by | one | 11 |  |

|-------|----------|-----|-----|-------|----|-----|----|--|

|       |          |     |     |       |    |     |    |  |

Four

As you can see 1 + 1 equal to 2 and two in binary (10) zero will be in the first digit and one is added to the one of the second digit. The same process is again happen so

| Four | 100 |

|------|-----|

| Five | 101 |

| Six  | 110 |

And so on up to millions.]

Some of you will ask me what is this number 100 is it one hundred or four? What is the answer?

Yes you will confuse between the two systems. Accordingly we will use the following:

100<sub>10</sub> The sub number  $_{10}$  mean this number is decimal, it is one hundred. 100<sub>2</sub> The sub number  $_2$  mean this number is binary, it is four in binary.

| 3  | 2  | 1  | 0  | الاس power                | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|---------------------------|---|---|---|---|---|

| 10 | 10 | 10 | 10 | المرتبة digit             | 2 | 2 | 2 | 2 | 2 |

|    |    |    |    | قيمة المرتبة digit values | 8 | 4 | 2 | 1 |   |

101012

$735_{10}$   $7*100+3*10+5*1=735_{10}$  $1*16+0*8+1*4+0*2+1*1=21_{10}$

**Example1:** Convert 9<sub>10</sub> to binary

|   |          | المتبقي من القسمة على ٢ |                   |

|---|----------|-------------------------|-------------------|

| 1 | 2 Result | Remain                  |                   |

| 9 | 4        | 1 1                     |                   |

| 4 | 2        | 0                       | 1001              |

| 2 | 1        | 0                       | $\longrightarrow$ |

| 1 | 0        | 1                       |                   |

Example 2: Convert 21<sub>10</sub> to binary

المتبقى من القسمة على ٢ Remain Result /2 21 101 5 2 1 0  $10101 \Rightarrow = 21_{10}$ 10 5 1 0 2 1 0 1

| Example 3:   | 21.3610        | and      | 101.    | 101 <sub>2</sub>  |               |

|--------------|----------------|----------|---------|-------------------|---------------|

| 21.3610      |                |          |         | 101               | .1012         |

| 2*10+1*1+3*  | 0.1 + 6 * 0.01 | 1*4+0*2+ | 1*1+1*1 | /2+0*1/4-         | +1*1/8        |

| 20 + 1 + 0.3 | + 0.06         | 4 -      | + 0 + 1 | $+ \frac{1}{2} +$ | 0 + 1/8       |

|              |                | 4        | + 0 + 1 | +0.5+             | 0 + 0.125     |

|              |                |          | So      | 101.1012          | $=5.625_{10}$ |

| Example 4: Convert 5.62510 to binar | Example 4 | : Convert | 5.62510 to | binary |

|-------------------------------------|-----------|-----------|------------|--------|

|-------------------------------------|-----------|-----------|------------|--------|

| /2     | Result     | Remain |      |               |

|--------|------------|--------|------|---------------|

| 5      | 2          | 1 1    |      | 101           |

| 5<br>2 | 1          | 0      |      | $\rightarrow$ |

| 1      | 0          | 1      |      |               |

| 0.625  | *2 = 1.250 | 1      | 0.25 |               |

| 0.25   | *2 = 0.5   | 0      | 0.5  |               |

| 0.5    | *2 = 1     | 1 4    | 0    | 101.101<br>→  |

| 0.625 | *2 | = 1.250 | 1   | 0.25 | - 1. W. S. M. S |

|-------|----|---------|-----|------|-----------------------------------------------------------------------------------------------------------------|

| 0.25  | *2 | = 0.5   | 0   | 0.5  |                                                                                                                 |

| 0.5   | *2 | = 1     | 1 4 | 0    | 101.101                                                                                                         |

#### Addition and Subtraction in binary number system:

Example 5: Add 2 to 3 in binary system.

| Decimal | Binary   | Addition | 10 |

|---------|----------|----------|----|

| 2       | 102      | (1)0     |    |

| + 3     | $+ 11_2$ | + 1/1    |    |

| 5       |          | 101      |    |

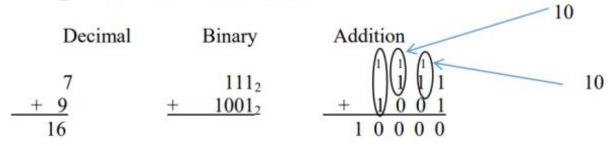

Example 6: Add 7 to 9 in binary system.

Example 7: Subtact 2 from 3 in binary system.

| Decimal | Bi  | nary  | Additio | on |   |

|---------|-----|-------|---------|----|---|

| 3       |     | 112   |         | 1  | 1 |

| - 2     | -   | 102   | -       | 1  | 0 |

| 1       | 275 | 00043 |         | 0  | 1 |

Example 8: Subtact 4 to 3 in binary system.

| Decimal | Binary        | Addition |

|---------|---------------|----------|

|         |               | P        |

|         |               | 1 10     |

|         |               | P        |

| 4       | 1002          | 100      |

| - 3     | <u>- 11</u> 2 | - 11     |

| 1       |               | 0 0 1    |

Multiplying and Division in binary system:

Example 9: Multiply 2 by 3 in binary system.

| Ι | Decimal | I | Binary   | Mu | ltiplication |

|---|---------|---|----------|----|--------------|

|   | 2       |   | 102      |    | 1 0          |

| * | 3       | * | $11_{2}$ | 3  | * <u>11</u>  |

|   |         |   |          |    | 1 0          |

|   |         |   |          | +  | 10 .         |

|   |         |   |          |    | 1 1 0        |

Example 10: Multiply 9 by 5 in binary system

| Γ | Decimal | 1 | Binary | Mu  | ltiplicat | ion      |

|---|---------|---|--------|-----|-----------|----------|

|   | 9       |   | 10012  |     | 100       | 1        |

| * | 5       | * | 1012   | *   | 1 0 1     | <u>l</u> |

|   | 45      |   | -      |     | 100       | 1        |

|   |         |   |        | 0 ( | 000       |          |

|   |         |   | +      | 100 | 1         |          |

|   |         |   |        | 1 0 | 1 1 0 1   | = 45     |

32\*1+0\*16+1\*8+1\*4+0\*2+1\*1=45

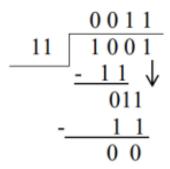

#### Example 11: Divide 9 by 3 in binary system

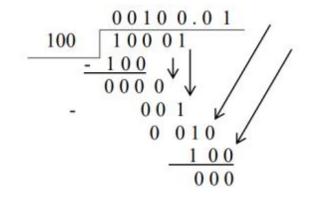

**Example 12:** Divide  $17_{10}$  by  $4_{10}$  in binary system

Answer  $17/4 = 100.01_2 = 4.25_{10}$

Ninevah University College of Electronics .Communication Dept

# Digital Technique Lec -2

Digital Technique is a subject that helps you to understand binary numbers and give the students good information about the most famous digital circuits that were used in every digital system.

2023-2022

#### Lecure 2

### **Octal and Hexadecimal System Numbers**

Octal and hexadecimal systems are used in software and in printing data.

Octal number system consists of 8 symbols They are 0, 1, 2, 3, 4, 5, 6, 7

Hexadecimal number system consists of 16 symbols They are 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, FWhere A=10, B=11, C=12, .....F=15. Any number in hexadecimal number may be written in this form 169<sub>16</sub> or 169H where **H** mean a symbol the same of sub 16.

For any number used in any system there are some information that must be known:

In Decimal number system 954 :

9 5 4  $9*10^2$   $5*10^1$   $4*1^0$  So the **base** of this number is 10 or we called it as radix.

In binary number system 101:

$\begin{array}{cccc} 1 & 0 & 1 \\ 1^{*}2^{2} & 0^{*}2^{1} & 1^{*}2^{0} \end{array}$  So the **base or the radix** of this number is 2.

What are the base for these system? Hexadecimal and Octal

For Hexadecimal radix=16 Octal radix=8

Q/ What is the radix and its value of the hexadecimal number  $15_{16}$ ?

Q/ Convert the following number 1F6AH to decimal

Q/What are the values of (1001) in Decimal, Octal and Hexadecimal?

Dec.  $1*10^{3}+0*10^{2}+0*10^{1}+1*10^{0} = 1001_{10}$

Oct.  $1*8^{3}+0*8^{2}+0*8^{1}+1*8^{0}=1*512+0+0+1 = 513_{10}$

Hex.  $1*16^{3}+0*16^{2}+0*16^{1}+1*16^{0}=4096+0+0+1=4097_{10}$

As you can note that any symbol of Octal number can be represented by 3 digit of binary number. Why? Because the largest number in octal is 7 and 7 in binary is 111

$7_8 = 111_2$  $3_8 = 011_2$

Q/ Convert 517<sub>8</sub> to binary number 5 1 7 101 001 111  $517_8=101001111_2$

This rule is also used for hexadecimal. Any digit in hexadecimal can be represented by 4 digits in binary number.

Q/ Convert F5E2H to binary number F 5 E 2 1111 0101 1110 0010 F5E2<sub>16</sub> =  $1111010111100010_2$

| Decimal | Binay | Oct. | Hex. | BCD       | Excess-3  |       |

|---------|-------|------|------|-----------|-----------|-------|

|         |       |      |      |           |           | Gray  |

| 0       | 0     | 0    | 0    | 0000 0000 | 0011 0011 | 0     |

| 1       | 1     | 1    | 1    | 0000 0001 | 0011 0100 | 1     |

| 2       | 10    | 2    | 2    | 0000 0010 | 0011 0101 | 11    |

| 3       | 11    | 3    | 3    | 0000 0011 | 0011 0110 | 10    |

| 4       | 100   | 4    | 4    | 0000 0100 | 0011 0111 | 110   |

| 5       | 101   | 5    | 5    | 0000 0101 | 0011 1000 | 111   |

| 6       | 110   | 6    | 6    | 0000 0110 | 0011 1001 | 101   |

| 7       | 111   | 7    | 7    | 0000 0111 | 0011 1010 | 100   |

| 8       | 1000  | 10   | 8    | 0000 1000 | 0011 1011 | 1100  |

| 9       | 1001  | 11   | 9    | 0000 1001 | 0011 1100 | 1101  |

| 10      | 1010  | 12   | Α    | 0001 0000 | 0100 0011 | 1111  |

| 11      | 1011  | 13   | В    | 0001 0001 | 0100 0100 | 1110  |

| 12      | 1100  | 14   | С    | 0001 0010 | 0100 0101 | 1010  |

| 13      | 1101  | 15   | D    | 0001 0011 | 0100 0110 | 1011  |

| 14      | 1110  | 16   | E    | 0001 0100 | 0100 0111 | 1001  |

| 15      | 1111  | 17   | F    | 0001 0101 | 0100 1000 | 1000  |

| 16      | 10000 | 20   | 10   | 0001 0110 | 0100 1001 | 11000 |

| 17      | 10001 | 21   | 11   | 0001 0111 | 0100 1010 | 11001 |

Table 1: Many system are written in this table

## Binary Coded Decimal (BCD or 8421 code)

This type of number system is a decimal number but it is written with binary symbols. Each digit of decimal must be written with 4

symbol of binary number. Why? That is because the largest symbol in decimal is 9 and this number in binary is 1001 so its four.

Example: 721<sub>10</sub>

0111 0010 0001 the space between the digits must be exist. If you write 721 = 011100100001 this is wrong because there are no space between digits.

Note:-

| Any digit in binary is called       | (bit)    |

|-------------------------------------|----------|

| Each four bits in binary is called  | (nibble) |

| Each eight bits in binary is called | (byte)   |

#### **BCD** Code

- A number with k decimal digits will require 4k bits in BCD.

- Decimal 396 is represented in BCD with 12bits as 0011 1001 0110, with each group of 4 bits representing one decimal digit.

- A decimal number in BCD is the same as its equivalent binary number only when the number is between 0 and 9.

- The binary combinations 1010 through 1111 are not used and have no meaning in BCD.

#### **Binary-Coded Decimal (BCD)**

| Decimal<br>Symbol | BCD<br>Digit |

|-------------------|--------------|

| 0                 | 0000         |

| 1                 | 0001         |

| 2                 | 0010         |

| 3                 | 0011         |

| 4                 | 0100         |

| 5                 | 0101         |

| 6                 | 0110         |

| 7                 | 0111         |

| 8                 | 1000         |

| 9                 | 1001         |

#### **Example:** Consider decimal 185 and its corresponding value in BCD and binary:

| $(185)_{10} = (0001\ 1000\ 01)$ | 01)       | $_{\rm BCD} = ($ | 101     | 11001) | 2         | If the binary<br>add 0110 to |

|---------------------------------|-----------|------------------|---------|--------|-----------|------------------------------|

|                                 | 4         | 0100             | 4       | 0100   | 8         | 1000                         |

|                                 | <u>+5</u> | +0101            | $\pm 8$ | +1000  | <u>+9</u> | +1001                        |

| BCD addition                    | 9         | 1001             | 12      | 1100   | 17        | 10001                        |

|                                 |           |                  |         | +0110  |           | +0110                        |

|                                 |           |                  |         | 10010  |           | 10111                        |

f the binary sum is greater than or equal to 1010, we add 0110 to obtain the correct BCD sum and a carry.

## **Excess-3 system number**

- The Excess-3 code is also called as XS-3 code.

- The Excess-3 code words are derived from the 8421 BCD code words adding (0011)2.

- It is non-weighted code used to express decimal numbers.

- Return to table 2 to compare between Exess-3 and Decimal.

Add number 0011

| Decimal number       | $\longrightarrow$ BCD | XS-3      |

|----------------------|-----------------------|-----------|

| Ex: 94 <sub>10</sub> | 1001 0100             | 1100 0111 |

;;;

Each 16 bits in binary is called (word)

Excess-3 system is the same as BCD but each digit equal to BCD+3:

It mean the zero number in BCD=0000 while zero in Ex-3= 0011

| 5 in BCD | =0101      | Ex-3= 1000            |

|----------|------------|-----------------------|

| 9        | =1001      | = 1100                |

| 12       | =0001 0010 | =0100 0101 and so on. |

Refer to table 1 for other examples.

## **Binary Codes**

| <ul> <li>Gray Code</li> </ul>           | Gray Code                                               |                       |          |

|-----------------------------------------|---------------------------------------------------------|-----------------------|----------|

| <ul> <li>The advantage</li> </ul>       | Gray<br>Code                                            | Decimal<br>Equivalent |          |

| code group cha                          | inges in going from                                     |                       |          |

| one number to                           | the next.                                               | 0000<br>0001          | 0        |

| Error detection.                        |                                                         | 0011                  | 2        |

|                                         |                                                         | 0010                  | 3        |

| <ul> <li>Representation of a</li> </ul> | analog data.                                            | 0110                  | 4        |

| <ul> <li>Low power design.</li> </ul>   |                                                         | 0111                  | 5        |

|                                         |                                                         | 0101                  | 6        |

|                                         |                                                         | 0100                  | 7        |

| Example 1                               | Example 2                                               | 1100                  | 8        |

|                                         | Example 2                                               | 1101                  | 9        |

| $ $ Binary $\longrightarrow$ Gray $ $   | Grav Binary                                             | 1111<br>1110          | 10<br>11 |

|                                         | $'  ' \mid \text{Oldy} \longrightarrow \text{Dilidity}$ |                       |          |

| 0010 0011                               |                                                         | 1010                  | 12       |

| 1011 1110                               | 0101 0110                                               | 1011                  | 13       |

| 1011 1110                               | 1100 1000                                               | 1001                  | 14       |

|                                         | 1100 1000                                               | 1000                  | 15       |

· Gray Code

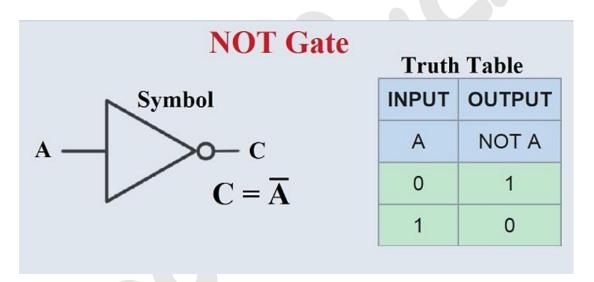

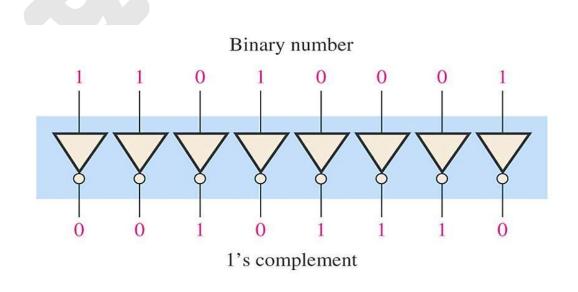

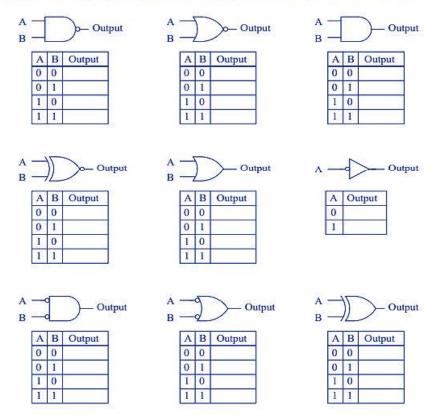

#### The Inverter (NOT Gate) •

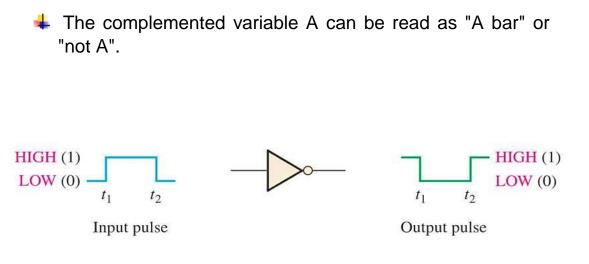

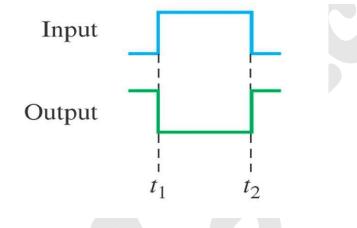

- The inverter (NOT gate) performs the operation called inversion or complementation.

- The inverter changes one logic level to the opposite level. In terms of bits, it changes a 1 to a 0 and a 0 to a 1.

- Standard logic symbol for the inverter as well as Inverter Truth Table are shown in Figure (1) below.

- When a HIGH level is applied to an inverter input, a LOW level will appear on its output.

- When a LOW level is applied to its input, a HIGH will appear on its output.

- > A table such as this is called a **truth table**.

- The operation of an inverter (NOT gate) can be expressed as follows:

- If the input variable is called A and the output variable is called  $\overline{Y}$ , then  $\overline{Y} = \overline{A}$ .

- This expression states that the output is the complement of the input, • So if A = 0, then Y =1, and if A = 1, then Y = 0. •

#### **Communication Dept 1st Class**

The inverter (NOT gate) is used in many applications. One of these application is to produce the 1's complement of an 8-bit(one byte) binary number. The bits of the binary number are applied to the inverter inputs and the 1's complement of the number appears on the output.

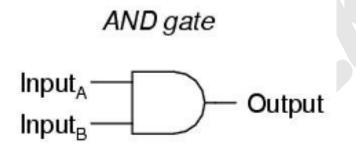

#### THE AND GATE

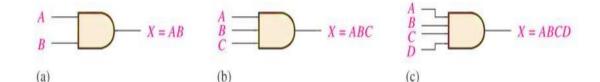

- The AND gate is one of the basic logic gates. An AND gate can have two or more inputs and performs what is known as "logical multiplication"

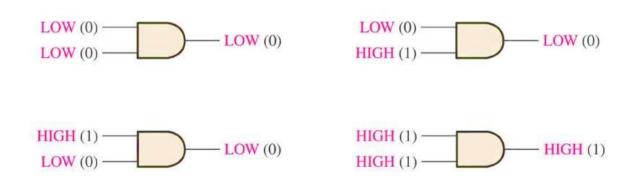

- Standard logic symbols for the AND gate are shown in Figure below as well as the truth table for a 2-input AND gate is shown in the table below.

| А | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

- An AND gate produces a HIGH output only when all of the inputs are HIGH. When any of the inputs is LOW, the output is LOW. Therefore, the basic purpose of an AND gate is to determine when certain conditions are simultaneously true, as indicated by HIGH levels on all of its inputs, and to produce a HIGH on its output to indicate that all these conditions are true.

- Assume the inputs of the 2-input AND gate are labeled A and B, and the output is labeled Y.

- The AND gate operation can be stated as follows:

For a 2-input AND gate, output Y is HIGH only when both inputs A and B are HIGH.

Y is LOW when either A or B is LOW, or when both A and B are LOW

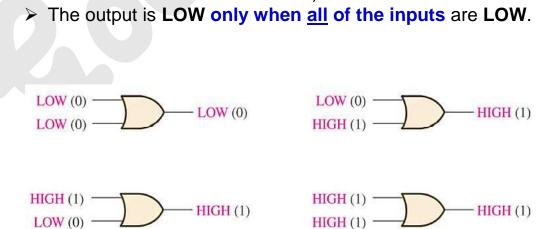

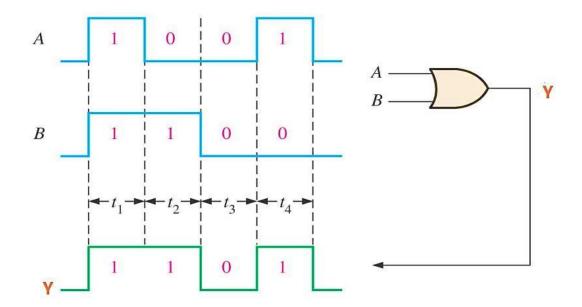

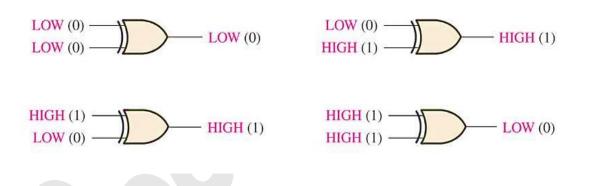

Two input waveforms, A and B, are applied to an X-OR gate inputs as in Figure below, Y is the resulting output waveform.

Figure below refers to the AND gate operation with a timing diagram showing input and output relationships.

## H.W

Develop the truth table for a 3-input AND gate?

- The logical AND function of two variables is represented mathematically either by placing a dot between the two variables, as A-B, or by simply writing the adjacent letters without the dot, as AB. We will normally use the latter notation because it is easier to write.

- The operation of a 2-input AND gate can be expressed in equation form as follows:

- If one input variable is A, the other input variable is B, and the output variable is Y, then the Boolean expression is:

#### Y = *AB*

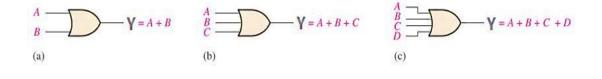

The figure below shows the AND gate logic symbol with two, three and four input variables and the equivalent output variable.

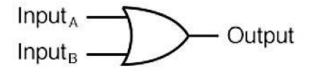

- The OR gate is another type of the basic gates from which all logic functions are constructed.

- An OR gate can have two or more inputs and performs what is known as logical addition.

- Standard logic symbol for the OR gate is shown in Figure below as well as the truth table of a 2-input OR gate is illustrated.

ronics Engineering

#### 2 - input OR gate

| А | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 1      |

- This truth table can be expanded for any number of inputs; but regardless of the number of inputs, the output is HIGH when one or more inputs are HIGH.

- > An OR gate can have any number of inputs greater than one.

- An OR gate produces a HIGH on the output when any of the inputs is HIGH (when either input A or input B is HIGH, or when both A and B are HIGH).

Two input waveforms, A and B, are applied to an OR gate inputs as in Figure below, Y is the resulting output waveform.

- The logical OR function of two variables is represented mathematically by a plus sign + between the two variables, for example, A + B.

- The operation of a 2-input OR gate can be expressed as follows:

- If one input variable is **A**, the other input variable is **B**, and if the output variable is **Y**, then the Boolean expression is as follows;  $\mathbf{Y} = \mathbf{A} + \mathbf{B}$

- The Figure below shows the OR gate logic symbol with two, three and four input variables and the output variable indicated.

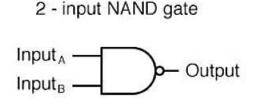

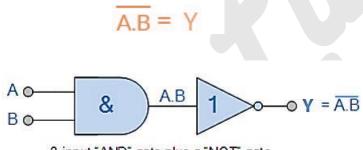

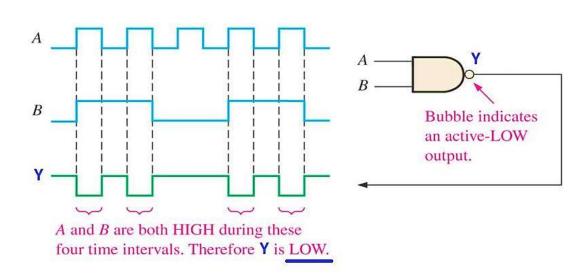

#### THE NAND GATE

- The NAND gate is a popular logic element because it can be used as a universal gate; that is, NAND gates can be used in combination to perform the AND, OR, and inverter gates.

- The term NAND is a contraction of NOT-AND and implies an AND function with a complemented (inverted) output.

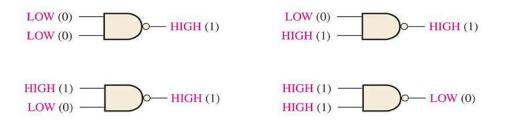

- The standard logic symbol for a 2-input NAND gate and its equivalency to an AND gate followed by an inverter are shown in Figure below, also the truth table of the logical operation of the 2-input NAND gate is shown in table below:

| А | В | Output |

|---|---|--------|

| 0 | 0 | 1      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 0      |

- For the specific case of a 2-input NAND gate, as shown in Figure above with the inputs labeled A and B and the output (Y), the operation can be stated as follows:

- For a 2-input NAND gate, output Y is LOW <u>only</u> when both inputs A and B are HIGH; Y output is HIGH when <u>either</u> A or B is LOW, <u>or when both</u> A and B are LOW.

**Communication Dept 1st Class**

That this operation is **opposite** to the <u>AND gate</u> in terms of the output level. In other words, The NAND is the same as AND except the output is **inverted**.

The NAND gate is equivalent to an AND gate followed by NOT (Invertor) as shown before. So the expression will be as follows, if the inputs are A and B, and the output is Y:

2-input "AND" gate plus a "NOT" gate

Two input waveforms, A and B, are applied to a NAND gate inputs as in Figure below, Y is the resulting output waveform.

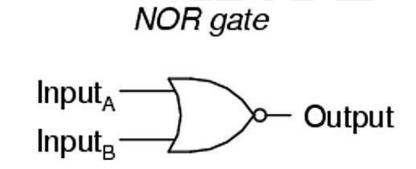

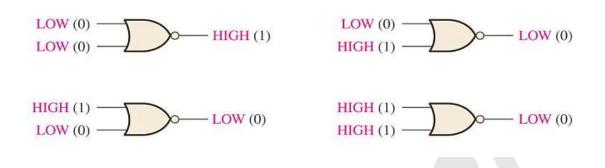

### THE NOR GATE

- The NOR gate, like the NAND gate, is a useful logic element because it can also be used as a universal gate; that is, NOR gates can be used in combination to perform the AND, OR, and inverter operations.

- The term NOR is a contraction of NOT-OR and implies an OR function with an inverted (complemented) output.

- The standard logic symbol for a 2-input NOR gate and its equivalent OR gate *followed by* an inverter are shown in Figure below. Also the truth table for a 2-input NOR gate is shown in the table below.

| Α | В | Output |

|---|---|--------|

| 0 | 0 | 1      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 0      |

As a result, the NOR is the same as the OR except the output is inverted.

A NOR gate produces a LOW output when any of its inputs is HIGH. Only when all of its inputs are LOW is the output HIGH. For a 2-input NOR gate, output X is <u>LOW</u> when either input A or input B is HIGH, or when both A and B are HIGH.

Y (output) is <u>HIGH only</u> when both A and B are LOW.

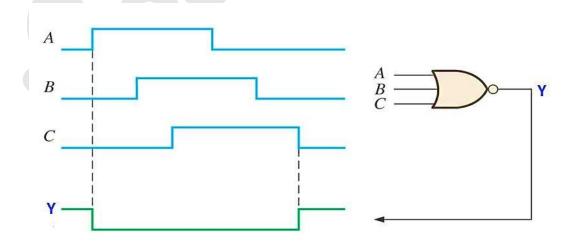

If three input waveforms, **A**, **B** and **C**, are applied to the NOR gate inputs as in Figure below, what is the resulting output waveform?

#### Solution:

The output **Y** is LOW when any input is HIGH as shown by the output waveform **Y** in the timing diagram

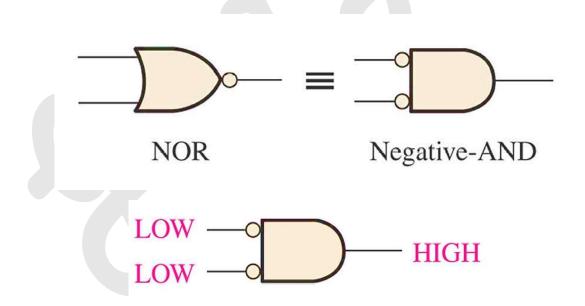

## NEGATIVE-AND EQUIVALENT OPERATION OF THE NOR GATE

- A NOR gate can be used for an AND operation that requires all LOW inputs to produce a HIGH output. This aspect of NOR operation is called **Negative-AND**.

- For a 2-input NOR gate performing a negative-AND operation, output Y is HIGH only when both inputs A and B are LOW.

- When a NOR gate is used to detect all LOWs on its inputs rather than one or more HIGHs, it is performing the negative-AND operation and is represented by the standard symbol in Figure below

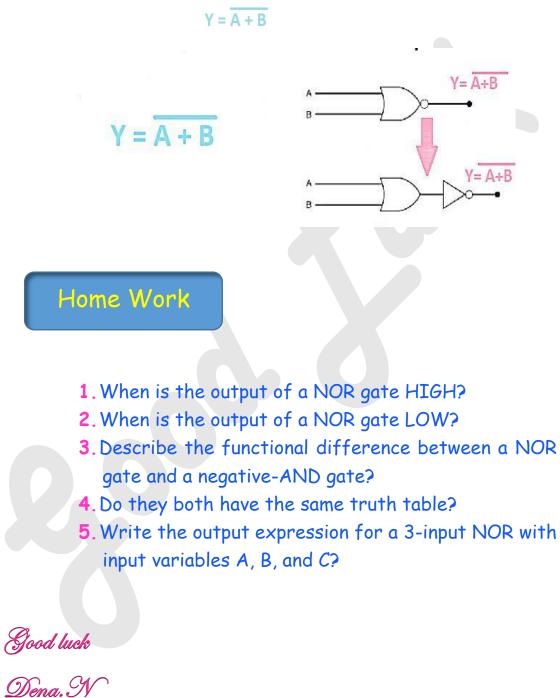

#### LOGIC EXPRESSION FOR A NOR GATE

The Boolean expression for the output of a 2-input NOR gate can be written as:

# **Logic Gates**

## XOR gate & XNOR-gate

LEC-2/Part2

## **First Class**

2022

By: Assistant Lecturer Dena Nameer

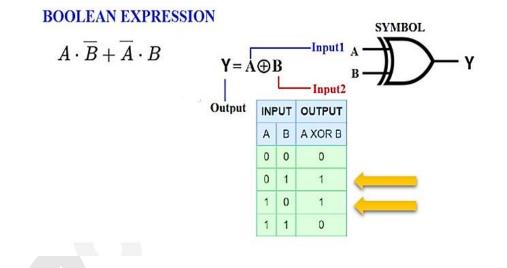

#### Exclusive-OR (XOR) gate

- The XOR gate has only two inputs.

- The output of an exclusive-OR gate is HIGH only when the two inputs are at opposite logic levels.

- This operation can be stated as follows with reference to inputs A and B and output Y:

- For an exclusive-OR gate, output Y is HIGH when input A is LOW and input B is • HIGH, or when input A is HIGH and input B is LOW; Y is LOW when both A and B are HIGH or LOW.

- Standard logic symbols for the exclusive OR (XOR) gate are shown in Figure below as well as the truth table for XOR gate is shown in table below:

## **XOR GATE**

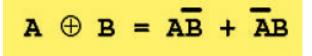

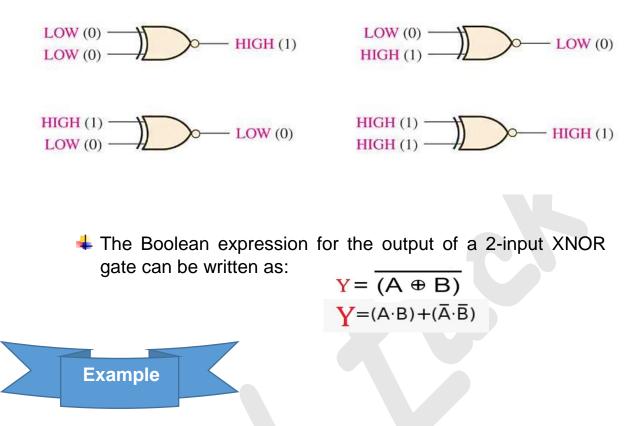

The Boolean expression for the output of a 2-input XOR gate can be written as:

As a result, we can make XOR gate by using NOT, AND, and OR gates as Figure below:

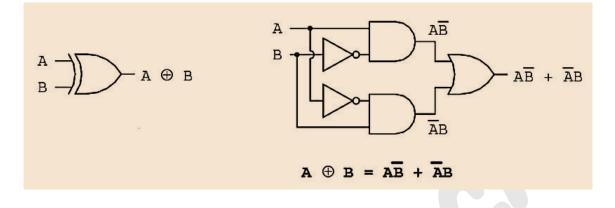

The four possible input combination and the resulting outputs for an XOR gate are illustrated in figure below:

Example of exclusive-OR gate operation with pulse waveform inputs.

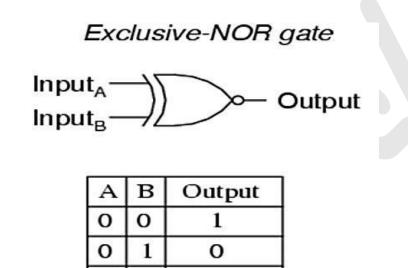

#### THE EXCLUSIVE-NOR GATES

The standard logic symbol for an exclusive-NOR (XNOR) gate and its equivalent exclusive-OR (XOR) gate followed by an inverter are shown in Figure below as well as the truth table for exclusive NOR (XNOR) gate is shown in table below:

0

1

2-input "Ex-OR" Gate plus a " NOT" Gate

> Like the XOR gate, an **XNOR** has only two inputs.

1

1

0

1

- The bubble on the output of the XNOR symbol indicates that its output is opposite that of the XOR gate.

- When the two input logic levels are opposite, the output of the exclusive-NOR gate is LOW.

- For an exclusive-NOR gate, output Y is LOW when input A is LOW and input B is HIGH, or when A is HIGH and B is LOW; Y is HIGH when both A and B are HIGH or LOW.

**Electronics Engineering**

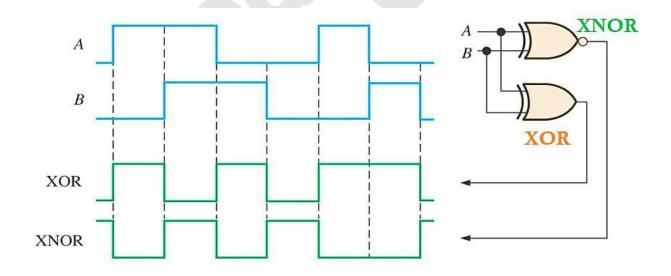

Determine the output waveforms for the XOR gate and for the XNOR gate, given the input waveforms, A and B, in Figure below?

<u>Solution</u>: the XOR output is HIGH only when both inputs are at opposite levels and the XNOR output is HIGH only when both inputs are the same levels.

# Symbols and truth tables for logic gates (limited to 2 inputs)

| _ | Name                                         | Graphic<br>symbol | Algebraic<br>function          | Truth<br>table                                                                                                                                        |

|---|----------------------------------------------|-------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| > | AND X-                                       | F                 | F = xy                         | $\begin{array}{c cccc} x & y & F \\ \hline 0 & 0 & 0 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \\ 1 & 1 & 1 \end{array}$                                              |

|   | OR X-<br>y-                                  | F                 | F = x + y                      | $\begin{array}{c ccc} x & y & F \\ \hline 0 & 0 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 1 \end{array}$                                               |

| > | Inverter x-                                  | F                 | <i>F</i> = <i>x</i> ′          | x F<br>0 1<br>1 0                                                                                                                                     |

| > | Buffer <i>x</i> -                            | F                 | <i>F</i> = <i>x</i>            | x F<br>0 0<br>1 1                                                                                                                                     |

| > | NAND X-<br>y-                                | F                 | F = (xy)'                      | $\begin{array}{c cccc} x & y & F \\ \hline 0 & 0 & 1 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \end{array}$                                              |

| > | NOR $\begin{array}{c} x \\ y \\ \end{array}$ | F                 | F = (x + y)'                   | x         y         F           0         0         1           0         1         0           1         0         0           1         1         0 |

|   | Exclusive-OR x-<br>(XOR) y-                  | F                 | $F = xy' + x'y$ $= x \oplus y$ | $\begin{array}{c cccc} x & y & F \\ \hline 0 & 0 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \end{array}$                                              |

| > | Exclusive-NOR x<br>or y<br>equivalence       |                   | $F = xy + x'y$ $= x \odot y$   | $\begin{array}{c cccc} x & y & F \\ \hline 0 & 0 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \\ 1 & 1 & 1 \end{array}$                                              |

Digital logic gates

## Home Work

- 1. When is the output of an XOR gate HIGH?

- 2. When is the output of an XNOR gate HIGH?

- 3. How can you use an XOR gate to detect when two bits are different?

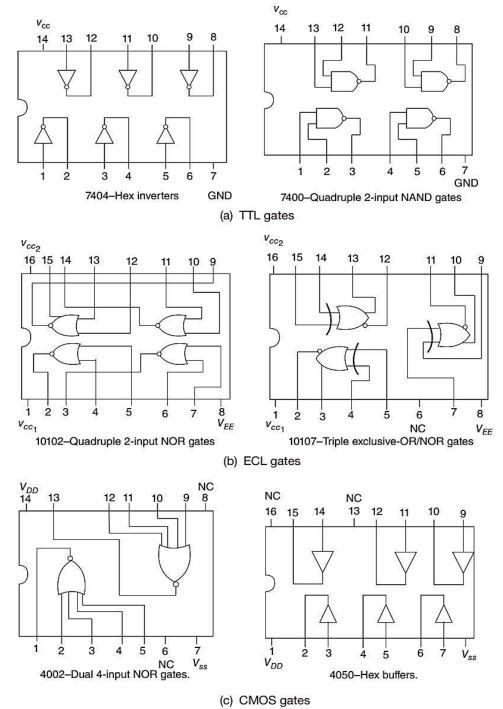

#### IC Digital Logic Families

Digital IC gates are classified not only by their logic operation, but also by the specific logic-circuit family to which they belong. Each logic family has its own basic electronic circuit upon which more complex digital circuits and functions are developed.

The basic circuit in each family is either a NAND or a NOR gate. The electronic components employed in the construction of the basic circuit are usually used to name the logic family.

Many different logic families of digital ICs have been introduced commercially. The ones that have achieved widespread popularity are listed below:

| TTL                      | Transistor-Transistor Logic                                           |

|--------------------------|-----------------------------------------------------------------------|

| ECL                      | Emitter-Coupled Logic                                                 |

| MOS                      | Metal-Oxide Semiconductor                                             |

| CMOS<br>I <sup>2</sup> L | Complementary Metal-Oxide Semiconductor<br>Integrated-injection Logic |

- **TTL** has an extensive list of digital functions and is currently the most popular logic family.

- *ECL* is used in systems requiring high-speed operations.

- MOS and I<sup>2</sup>L are used in circuits requiring high component density.

- **CMOS** is used in systems requiring low power consumption.

#### **Communication Dept 1st Class**

#### **Electronics Engineering**

Some typical integrated-circuit gates

Good luck Dena.N

## Introduction

George Boole, a nineteenth-century English Mathematician, developed a system of logical algebra by which reasoning can be expressed mathematically. In 1854, Boole published a classic book, "An Investigation of the Laws of thought" on which he founded the Mathematical theories of Logic and Probabilities, Boole"s system of logical algebra, now called Boolean algebra, was investigated as a tool for analyzing and designing relay switching circuits by Claude E. Shannon at the Massachusetts institute of Technology in 1938. Shannon, a research assistant in the Electrical Engineering Department, wrote a thesis entitled "A" symbolic Analysis of Relay and Switching Circuits. As a result of his work, Boolean algebra is now, used extensively in the analysis and design of logical circuits. Today Boolean algebra is the backbone of computer circuit analysis.

# **Two Valued Logical Symbol:**

The electronics circuits and signals

- A logic 1 will represent closed switch, a high voltage, or an "on" lamp.

- A logic 0 will represent an open switch, low voltage, or an "off" lamp.

These describe the only two states that exist in digital logic systems and will be used to represent the in and out conditions of logic gates.

## Fundamental Concepts of Boolean Algebra:

Boolean algebra is a logical algebra in which symbols are used to represent logic levels. Any symbol can be used, however, letters of the alphabet are generally used. Since the logic levels are generally associated with the symbols 1 and 0, whatever letters are used as variables that can take the values of 1 or 0.

Boolean algebra has only two mathematical operations, <u>addition</u> and <u>multiplication</u>. These operations are associated with the OR gate and the AND gate, respectively.

# **Logical Addition:**

When the + (the logical addition) symbol is placed between two variables, say X and Y, since both X and Y can take only the role **0** and **1**, we can define the + Symbol by listing, all possible combinations for X and Y and the resulting value of X + Y.

The possible input and output combinations may arranged as follows:

0 + 0 = 0 0 + 1 =1 1 + 0 = 1 1 + 1 = 1

This table represents a standard binary addition, except for the last entry. When both X and Y represents 1"s, the value of X + Y is 1. The symbol + therefore does not has the "**Normal**" meaning, but is a Logical addition symbol. The plus symbol (+) read as "**OR**", therefore X + Y is read as X or Y.

# **Logical Multiplication:**

We can define the "." (logical multiplication) symbol or AND operator by listing all possible combinations for (input) variables X and Y and the resulting (output) value of X . Y as,

Note

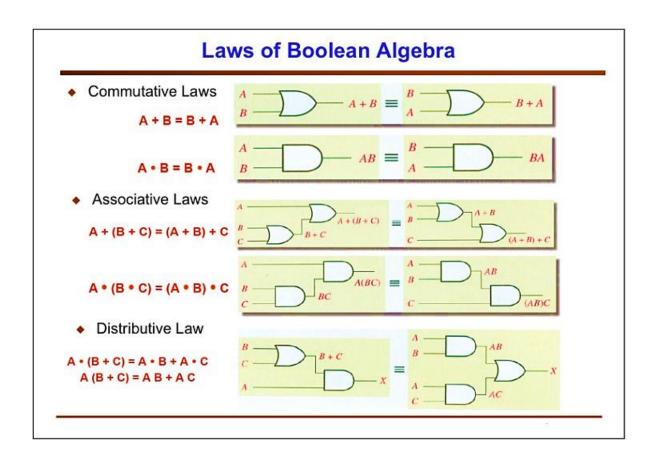

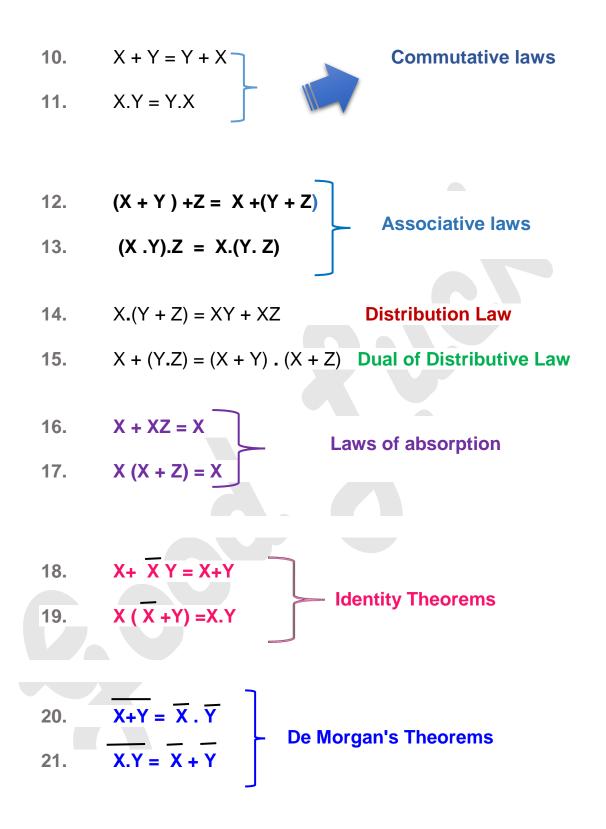

Three of the basic laws of Boolean algebra are the same as in ordinary algebra; the commutative law, the associative law and the distributive law.

The commutative law: for addition and multiplication of two variables is written as,

$$A + B = B + A$$

And  $A \cdot B = B \cdot A$

The associative law: for addition and multiplication of three variables is written as,

$$(A + B) + C = A + (B + C)$$

And (A.B). C = A. (B. C)

The distributive law: for three variables involves, both addition and multiplication and is written as,

A (B+C) = A B + AC

**Note** that while either '+' and "." s can be used freely. The two cannot be mixed without ambiguity in the absence of further rules. For example does A  $\cdot$  B + C means (A  $\cdot$  B) + C or A  $\cdot$  (B+ C)?

These two form different values for A = 0, B = 1 and C = 1, because we have

$(A \cdot B) + C = (0.1) + 1 = 1$ and A  $(B + C) = 0 \cdot (1 + 1) = 0$

which are different. The rule which is used is that "." is always performed before '+'. Thus X . Y + Z is (X.Y) + Z.

#### **Basic Duality in Boolean Algebra:**

We state the duality theorem without proof. Starting with a Boolean relation, we can derive another Boolean relation by

1) Changing each OR (+) sign to an AND (.) sign.

2) Changing each AND (.) sign to an OR (+) sign.

3) Complementary each 0 and 1 For instance.

**Electronics Engineering**

The dual relation is

Also since A(B+C) = AB + AC by distributive law.

Its dual relation is A + B C = (A + B) (A + C)

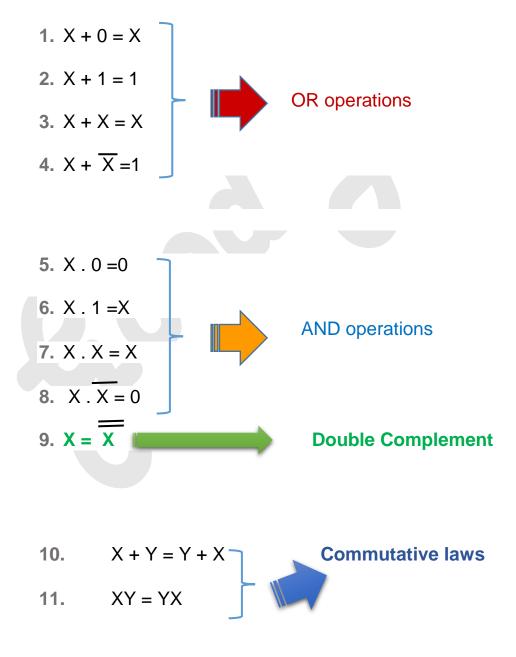

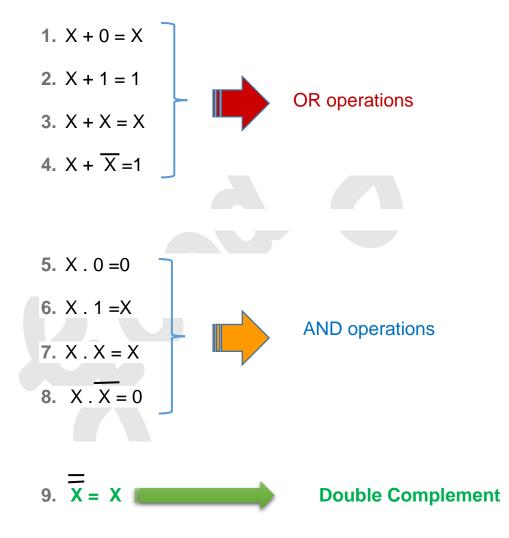

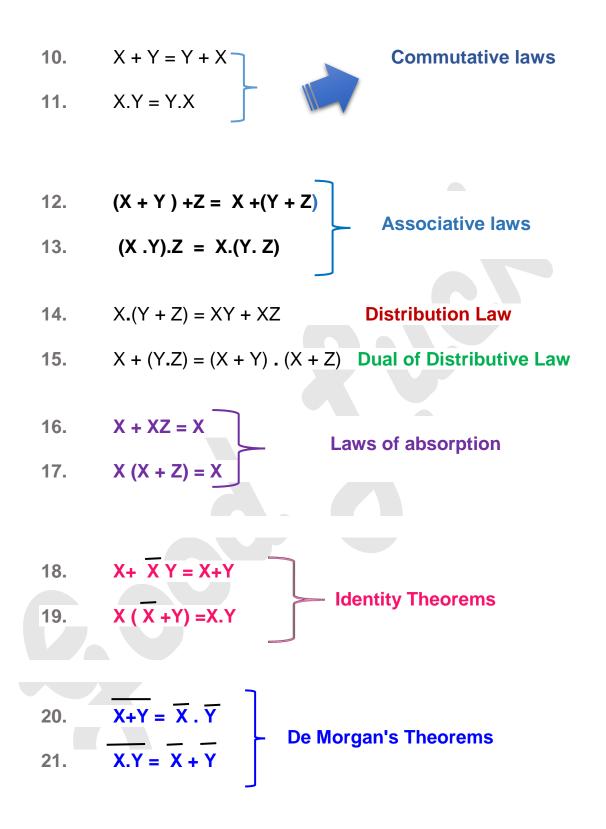

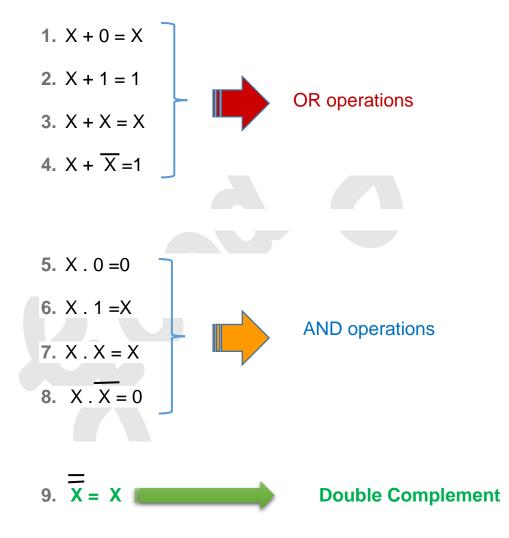

### **Fundamental Laws and Theorems of Boolean Algebra:**

**Electronics Engineering**

| 12. | (X + Y ) +Z= X +(Y + Z)<br>Associative laws                             |

|-----|-------------------------------------------------------------------------|

| 13. | (X .Y).Z =X.(Y. Z)                                                      |

| 14. | X (Y + Z) = XY + XZ <b>Distribution Law</b>                             |

| 15. | X + Y.Z = (X + Y) . (X + Z) Dual of Distributive Law                    |

| 16. | X + XZ = X<br>Laws of absorption                                        |

| 17. | X (X + Z) = X                                                           |

| 18. | $X + \overline{X} Y = X + Y$                                            |

| 19. | X (X +Y) =X.Y                                                           |

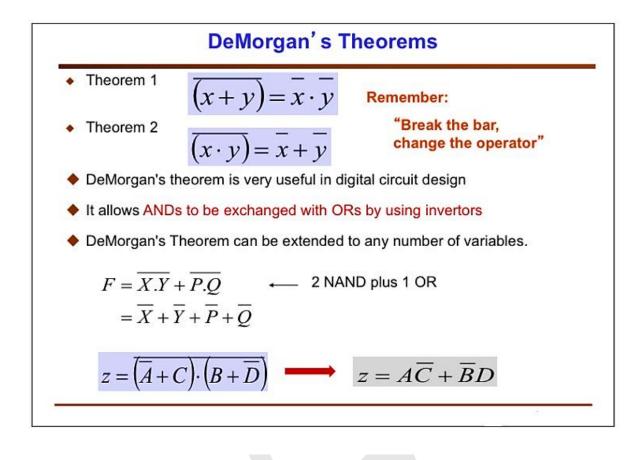

| 20. | $\overline{X+Y} = \overline{X} \cdot \overline{Y}$ De Morgan's Theorems |

| 21. | 21. $\overline{X.Y} = \overline{X} + \overline{Y}$                      |

Good luck Dena.N

## Introduction

George Boole, a nineteenth-century English Mathematician, developed a system of logical algebra by which reasoning can be expressed mathematically. In 1854, Boole published a classic book, "An Investigation of the Laws of thought" on which he founded the Mathematical theories of Logic and Probabilities, Boole"s system of logical algebra, now called Boolean algebra, was investigated as a tool for analyzing and designing relay switching circuits by Claude E. Shannon at the Massachusetts institute of Technology in 1938. Shannon, a research assistant in the Electrical Engineering Department, wrote a thesis entitled "A" symbolic Analysis of Relay and Switching Circuits. As a result of his work, Boolean algebra is now, used extensively in the analysis and design of logical circuits. Today Boolean algebra is the backbone of computer circuit analysis.

# **Two Valued Logical Symbol:**

The electronics circuits and signals

- A logic 1 will represent closed switch, a high voltage, or an "on" lamp.

- A logic 0 will represent an open switch, low voltage, or an "off" lamp.

These describe the only two states that exist in digital logic systems and will be used to represent the in and out conditions of logic gates.

## Fundamental Concepts of Boolean Algebra:

Boolean algebra is a logical algebra in which symbols are used to represent logic levels. Any symbol can be used, however, letters of the alphabet are generally used. Since the logic levels are generally associated with the symbols 1 and 0, whatever letters are used as variables that can take the values of 1 or 0.

Boolean algebra has only two mathematical operations, <u>addition</u> and <u>multiplication</u>. These operations are associated with the OR gate and the AND gate, respectively.

# **Logical Addition:**

When the + (the logical addition) symbol is placed between two variables, say X and Y, since both X and Y can take only the role **0** and **1**, we can define the + Symbol by listing, all possible combinations for X and Y and the resulting value of X + Y.

The possible input and output combinations may arranged as follows:

0 + 0 = 0 0 + 1 =1 1 + 0 = 1 1 + 1 = 1

This table represents a standard binary addition, except for the last entry. When both X and Y represents 1"s, the value of X + Y is 1. The symbol + therefore does not has the "**Normal**" meaning, but is a Logical addition symbol. The plus symbol (+) read as "**OR**", therefore X + Y is read as X or Y.

# **Logical Multiplication:**

We can define the "." (logical multiplication) symbol or AND operator by listing all possible combinations for (input) variables X and Y and the resulting (output) value of X . Y as,

Note

Three of the basic laws of Boolean algebra are the same as in ordinary algebra; the commutative law, the associative law and the distributive law.

The commutative law: for addition and multiplication of two variables is written as,

$$A + B = B + A$$

And  $A \cdot B = B \cdot A$

The associative law: for addition and multiplication of three variables is written as,

$$(A + B) + C = A + (B + C)$$

And (A.B). C = A. (B. C)

The distributive law: for three variables involves, both addition and multiplication and is written as,

A (B+C) = A B + AC

**Note** that while either '+' and "." s can be used freely. The two cannot be mixed without ambiguity in the absence of further rules. For example does A  $\cdot$  B + C means (A  $\cdot$  B) + C or A  $\cdot$  (B+ C)?

These two form different values for A = 0, B = 1 and C = 1, because we have

$(A \cdot B) + C = (0.1) + 1 = 1$ and A  $(B + C) = 0 \cdot (1 + 1) = 0$

which are different. The rule which is used is that "." is always performed before '+'. Thus X . Y + Z is (X.Y) + Z.

#### **Basic Duality in Boolean Algebra:**

We state the duality theorem without proof. Starting with a Boolean relation, we can derive another Boolean relation by

1) Changing each OR (+) sign to an AND (.) sign.

2) Changing each AND (.) sign to an OR (+) sign.

3) Complementary each 0 and 1 For instance.

**Electronics Engineering**

The dual relation is

| Also since | A (B + C) = AB + AC | by distributive law. |

|------------|---------------------|----------------------|

|            |                     |                      |

Its dual relation is A + B C = (A + B) (A + C)

## **Fundamental Laws and Theorems of Boolean Algebra:**

**Electronics Engineering**

5

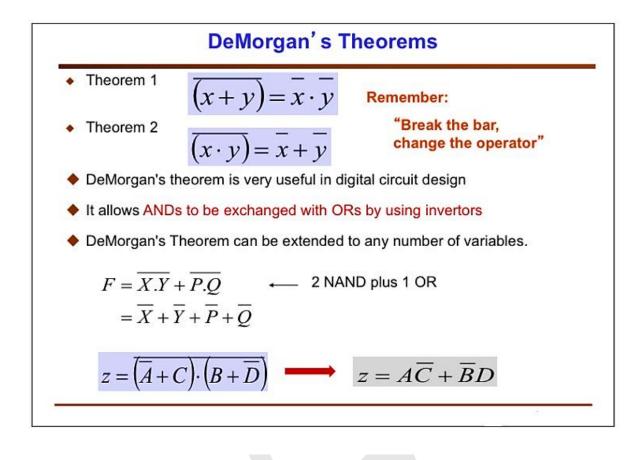

**De'Morgan's Theorems** is important to Boolean logic. They allow us to **exchange OR operation with AND operation and vice versa**. Applying De'Morgan, we can also simplify Boolean expression in many cases.

Good luck Dena N

## Introduction

George Boole, a nineteenth-century English Mathematician, developed a system of logical algebra by which reasoning can be expressed mathematically. In 1854, Boole published a classic book, "An Investigation of the Laws of thought" on which he founded the Mathematical theories of Logic and Probabilities, Boole"s system of logical algebra, now called Boolean algebra, was investigated as a tool for analyzing and designing relay switching circuits by Claude E. Shannon at the Massachusetts institute of Technology in 1938. Shannon, a research assistant in the Electrical Engineering Department, wrote a thesis entitled "A" symbolic Analysis of Relay and Switching Circuits. As a result of his work, Boolean algebra is now, used extensively in the analysis and design of logical circuits. Today Boolean algebra is the backbone of computer circuit analysis.

# **Two Valued Logical Symbol:**

The electronics circuits and signals

- A logic 1 will represent closed switch, a high voltage, or an "on" lamp.

- A logic 0 will represent an open switch, low voltage, or an "off" lamp.

These describe the only two states that exist in digital logic systems and will be used to represent the in and out conditions of logic gates.

## Fundamental Concepts of Boolean Algebra:

Boolean algebra is a logical algebra in which symbols are used to represent logic levels. Any symbol can be used, however, letters of the alphabet are generally used. Since the logic levels are generally associated with the symbols 1 and 0, whatever letters are used as variables that can take the values of 1 or 0.

Boolean algebra has only two mathematical operations, <u>addition</u> and <u>multiplication</u>. These operations are associated with the OR gate and the AND gate, respectively.

# **Logical Addition:**

When the + (the logical addition) symbol is placed between two variables, say X and Y, since both X and Y can take only the role **0** and **1**, we can define the + Symbol by listing, all possible combinations for X and Y and the resulting value of X + Y.

The possible input and output combinations may arranged as follows:

0 + 0 = 0 0 + 1 =1 1 + 0 = 1 1 + 1 = 1

This table represents a standard binary addition, except for the last entry. When both X and Y represents 1"s, the value of X + Y is 1. The symbol + therefore does not has the "**Normal**" meaning, but is a Logical addition symbol. The plus symbol (+) read as "**OR**", therefore X + Y is read as X or Y.

# **Logical Multiplication:**

We can define the "." (logical multiplication) symbol or AND operator by listing all possible combinations for (input) variables X and Y and the resulting (output) value of X . Y as,

Note

Three of the basic laws of Boolean algebra are the same as in ordinary algebra; the commutative law, the associative law and the distributive law.

The commutative law: for addition and multiplication of two variables is written as,

$$A + B = B + A$$

And  $A \cdot B = B \cdot A$

The associative law: for addition and multiplication of three variables is written as,

$$(A + B) + C = A + (B + C)$$

And (A.B). C = A. (B. C)

The distributive law: for three variables involves, both addition and multiplication and is written as,

A (B+C) = A B + AC

**Note** that while either '+' and "." s can be used freely. The two cannot be mixed without ambiguity in the absence of further rules. For example does A  $\cdot$  B + C means (A  $\cdot$  B) + C or A  $\cdot$  (B+ C)?

These two form different values for A = 0, B = 1 and C = 1, because we have

$(A \cdot B) + C = (0.1) + 1 = 1$ and A  $(B + C) = 0 \cdot (1 + 1) = 0$

which are different. The rule which is used is that "." is always performed before '+'. Thus X . Y + Z is (X.Y) + Z.

#### **Basic Duality in Boolean Algebra:**

We state the duality theorem without proof. Starting with a Boolean relation, we can derive another Boolean relation by

1) Changing each OR (+) sign to an AND (.) sign.

2) Changing each AND (.) sign to an OR (+) sign.

3) Complementary each 0 and 1 For instance.

**Electronics Engineering**

The dual relation is

| Also since | A (B + C) = AB + AC | by distributive law. |

|------------|---------------------|----------------------|

|            |                     |                      |

Its dual relation is A + B C = (A + B) (A + C)

## **Fundamental Laws and Theorems of Boolean Algebra:**

**Electronics Engineering**

5

**De'Morgan's Theorems** is important to Boolean logic. They allow us to **exchange OR operation with AND operation and vice versa**. Applying De'Morgan, we can also simplify Boolean expression in many cases.

Good luck Dena N

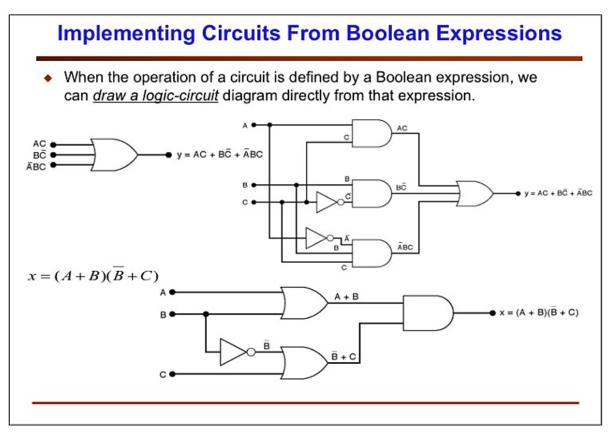

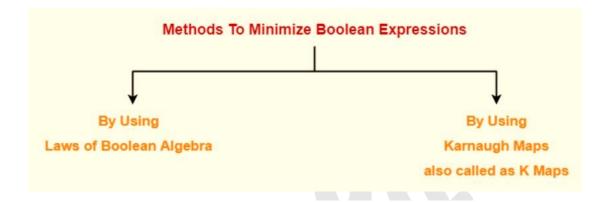

#### Methods to minimize Boolean expression:

- **1.** By using laws of Boolean Algebra.

- 2. By using Karnaugh Maps also called as K Maps.

#### Introduction for Karnaugh map

A K-map is a diagram made up of squares, with each square representing one minterm of the function that is to be minimized. Since any Boolean function can be expressed as a sum of minterms, it follows that a Boolean function is recognized graphically in the map from the area enclosed by those squares whose minterms are included in the function.

The Karnaugh Map also called as K Map is a graphical representation that provides a systematic method for simplifying the boolean expressions.

For a Boolean expression consisting of n-variables, number of cells required in  $K-Map = 2^n$  cells.

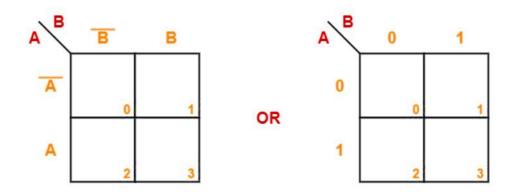

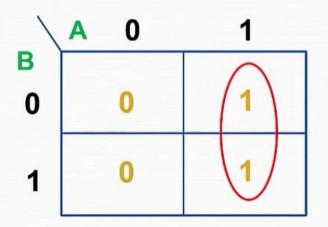

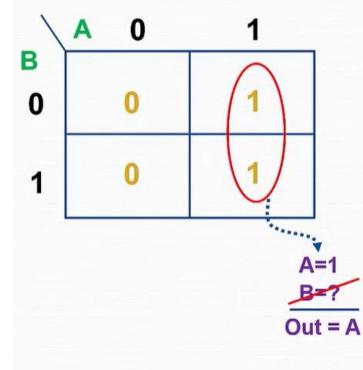

## **4** Two Variable K- Map

- Two variable K-Map is drawn for a Boolean expression consisting of two variables.

- > The number of cells present in two variable K-Map =  $2^2$  = 4 cells.

- So, for a Boolean function consisting of two variables, we draw a (2 x 2) K-Map.

Two variable K-Map may be represented as-

**Electronics Engineering**

#### Two Variable K Map

Here, **A** and **B** are the *two variables* of the given Boolean function.

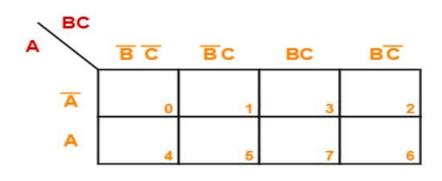

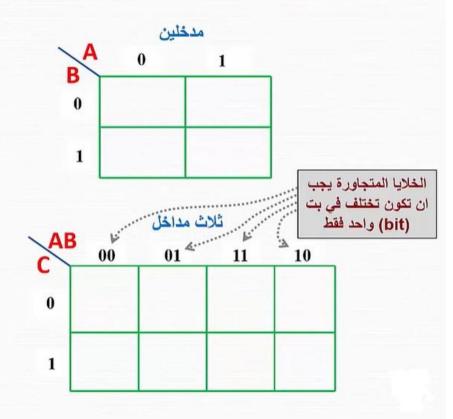

## **4** Three Variable K Map-

- Three variable K Map is drawn for a Boolean expression consisting of three variables.

- > The number of cells present in three variable K-Map =  $2^3 = 8$  cells.

- So, for a Boolean function consisting of three variables, we draw a (2 x 4) K Map.

Three variable K-Map may be represented as-

Three Variable K Map

Here, **A**, **B** and **C** are the three variables of the given Boolean function.

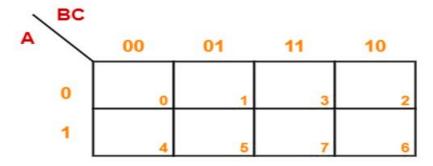

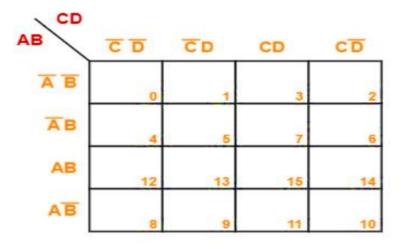

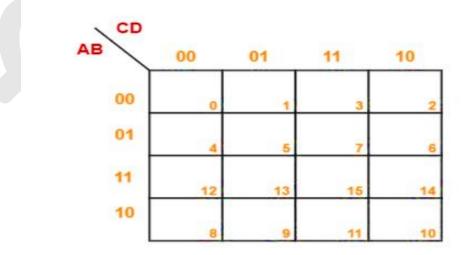

# **4** Four Variable K-Map-

- Four variable K-Map is drawn for a Boolean expression consisting of four variables.

- > The number of cells present in four variable K-Map =  $2^4$  = 16 cells.

- So, for a boolean function consisting of four variables, we draw a (4 x 4) K-Map.

Four variable K-Map may be represented as-

Four Variable K Map

Here, A, B, C and D are the four variables of the given Boolean function.

# Karnaugh Map Simplification Rules-

To minimize the given Boolean function

- We draw a K Map according to the number of variables it contains.

- We fill the K Map with 0's and 1's according to its function.

- Then, we minimize the function in accordance with the following steps to find the minterm solution or K-map:

#### ➢ <u>Step-1:</u>

Firstly, we define the given expression in its canonical form.

#### ➢ <u>Step-2:</u>

*Next*, we create the K-map by entering 1 to each product-term into the K-map cell and fill the remaining cells with zeros.

#### ➢ <u>Step-3:</u>

Next, we form the groups by considering each one in the K-map.

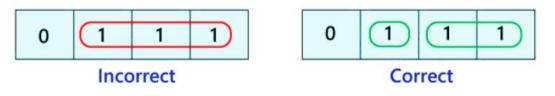

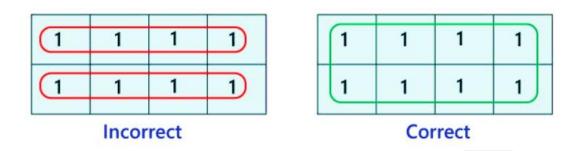

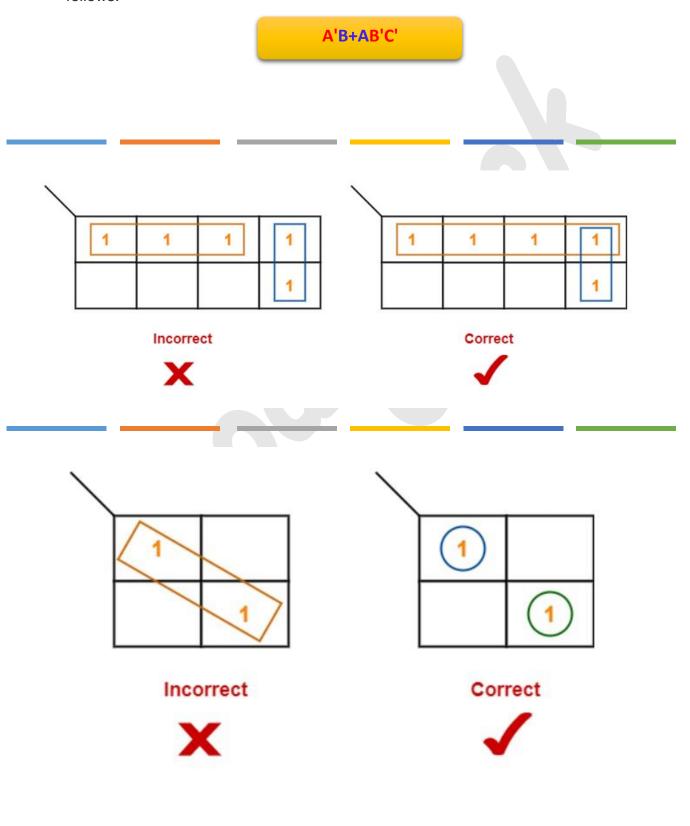

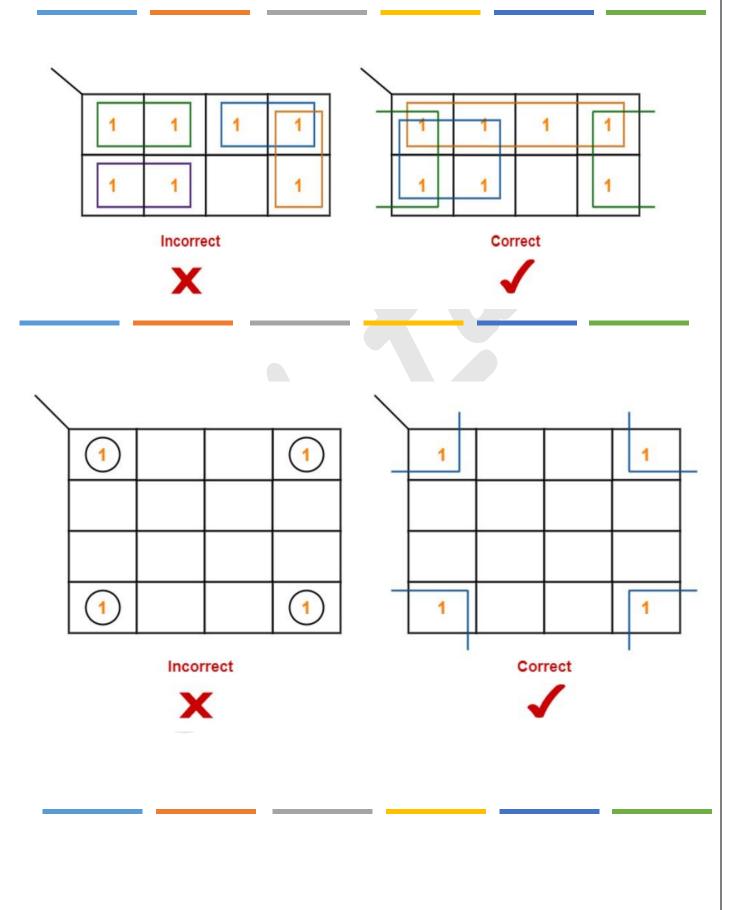

<u>Notice</u> that each group should have the largest number of 'ones'. A group cannot contain an empty cell or cell that contains 0.

- We can only create a group whose number of cells can be represented in the power of 2.

- In other words, a group can only contain 2n i.e. 1, 2, 4, 8, 16 and so on number of cells.

We group the number of ones in the decreasing order. First, we have to try to make the group of eight, then for four, after that two and lastly for 1.

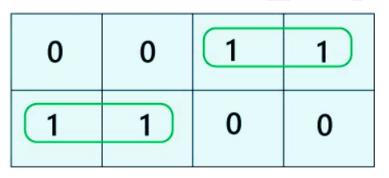

- **4** Groups can be only either horizontal or vertical.

- ✤ We cannot create groups of diagonal or any other shape.

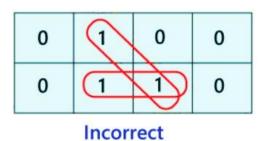

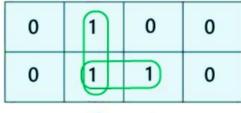

Correct

1

1

0

The elements in one group can also be used in different groups only when the size of the group is increased. In other words, each group should be as large as possible.

# 0 1 1

1

1

Incorrect

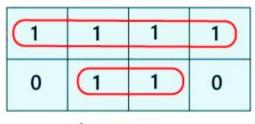

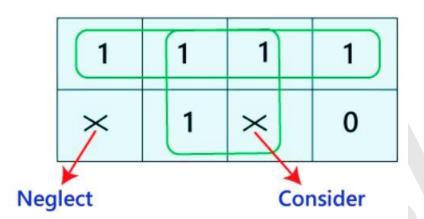

The elements located at the edges of the table are considered to be adjacent. So, we can group these elements.

| 1 | 0 | 0 | 1 |

|---|---|---|---|

| 1 | 0 | 0 | 1 |

We can consider the 'don't care condition' only when they aid in increasing the group-size. Otherwise, 'don't care' elements are discarded.

#### <u>Step 4:</u>

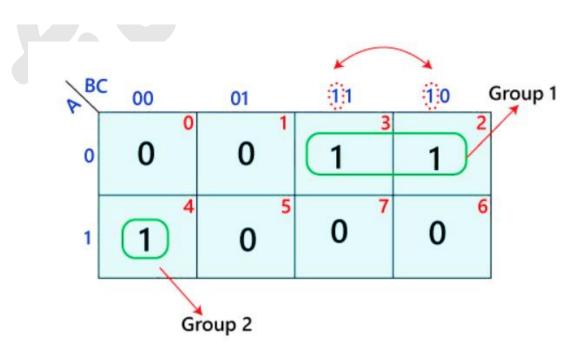

In the next step, we find the Boolean expression for each group. By looking at the common variables in cell-labeling, we define the groups in terms of input variables. In the below example, there is a total of **two groups**, i.e., group 1 and group 2, with two and one number of 'ones'.

In the first group, the ones are present in the row for which the value of A is 0. Thus, they contain the complement of variable A. Remaining two 'ones' are present in adjacent columns. In these columns, only B term in common is the product term corresponding to the group as (A'B).

Just like group 1, <u>in group 2</u>, the one's are present in a row for which the value of A is 1. So, the corresponding variables of this column are **B'C'**. The overall product term of this group is( **AB'C'**).

#### Step 5:

Lastly, we find the Boolean expression for the Output. To find the simplified Boolean expression in the SOP form, we combine the product-terms of **all** individual groups. So the simplified expression of the above k-map is as follows:

**Electronics Engineering**

Let's take some examples.

#### Example 1:

Simplify the Boolean function:

$F(x, y, z) = \sum (2, 3, 4, 5)$

$F(x, y, z) = \sum (2, 3, 4, 5) = xy' + x'y$

#### Example 2:

Simplify the Boolean function:

$F(w, x, y, z) = \sum (0, 1, 2, 4, 5, 6, 8, 9, 12, 13, 14)$

**Electronics Engineering**

The simplified function is:

$\mathsf{F} = \mathsf{y}' + \mathsf{w}'\mathsf{z}' + \mathsf{x}\mathsf{z}'$

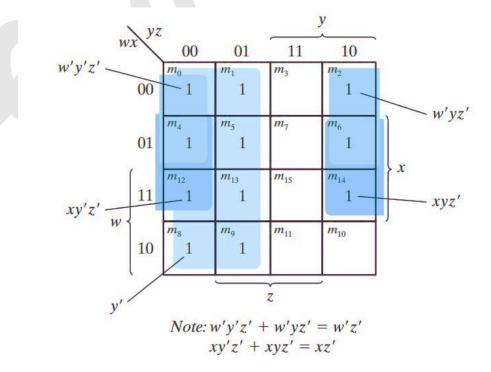

Map for Example 2,  $F(w, x, y, z) = \sum (0,1, 2, 4, 5, 6, 8, 9, 12, 13, 14)$

= y' + w'z' + xz'

Good luck Dena.N

LEC-1/Course-2

2022

By: Assistant Lecturer Dena Nameer

## **Digital Adder**

- In digital electronics an adder is a logic circuit that implements addition of numbers. In many computers and other types of processors, adders are used to calculate addresses, similar operations and table indices in the arithmetic logic unit (ALU) and also in other parts of the processors. These can be built for many numerical representations like binary coded decimal or excess-3.

- Adders are classified into two types:

- 1. Half adder

- 2. Full adder

Digital computers perform a variety of information-processing tasks. Among the functions encountered are the various arithmetic operations. The most basic arithmetic operation is the addition of two binary digits. This simple addition consists of four possible elementary operations:

✓ 0 + 0 = 0✓ 0 + 1 = 1✓ 1 + 0 = 1✓ 1 + 1 = 10

The first three operations produce a sum of one digit, but when both augend and addend bits are equal to 1, the binary sum consists of two digits. The higher significant bit of this result is called a **carry**. When the augend and addend numbers contain more significant digits, the carry obtained from the addition of two bits is added to the next higher order pair of significant bits. A combinational circuit that performs the addition of two bits is called a half adder. One that performs the addition of three bits (two significant bits and a previous carry) is a full adder. The names of the circuits stem from the fact that two half adders can be employed to implement a full adder.

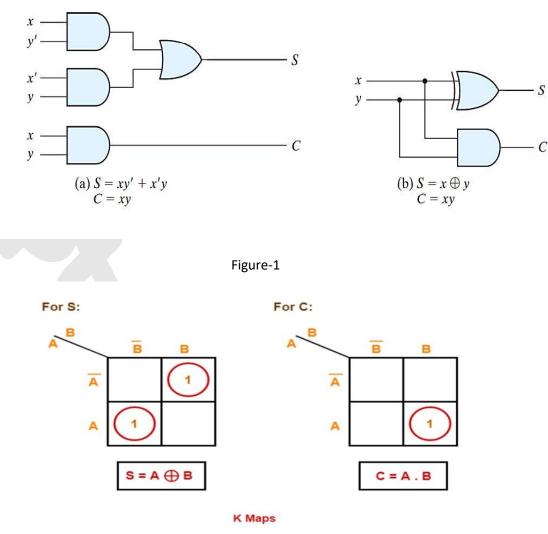

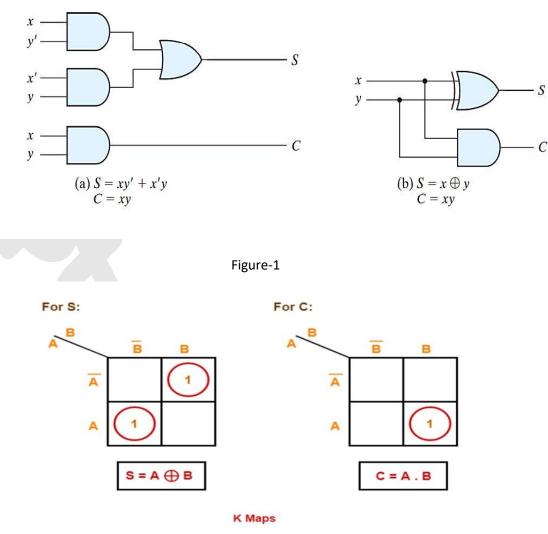

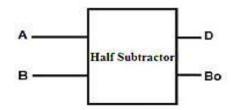

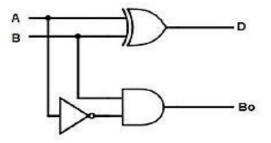

# Half Adder

From the verbal explanation of a half adder, we find that this circuit needs two binary inputs and two binary outputs. The input variables designate the augend and addend bits; the output variables produce the sum and carry. We assign symbols x and y to the two inputs and S (for sum) and C (for carry) to the outputs. The truth table for the half adder is listed below. The C output is 1 only when both inputs are 1. The S output represents the least significant bit of the sum. The simplified Boolean functions for the two outputs can be obtained directly from the truth table.

#### **Electronics Engineering**

| x | y | C | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

The simplified sum-of-products expressions are

S = X'Y + XY' C= XY

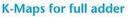

The logic diagram of the half adder implemented in sum of products is shown in Fig. 1-(a). It can be also implemented with an exclusive-OR and an AND gate as shown in Fig. 1-(b). This form is used to show that two half adders can be used to construct a full adder.

2

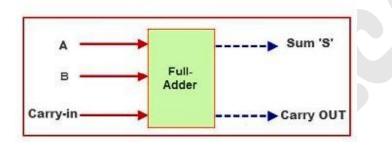

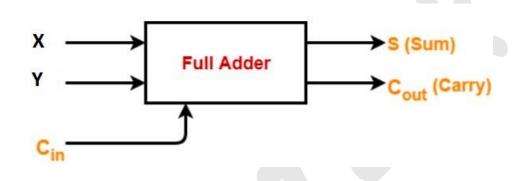

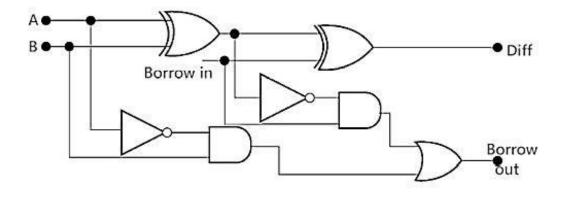

# Full Adder

Addition of n-bit binary numbers requires the use of a full adder, and the process of addition proceeds on a bit-by-bit basis, right to left, beginning with the least significant bit. After the least significant bit, addition at each position adds not only the respective bits of the words, but must also consider a possible carry bit from addition at the previous position.

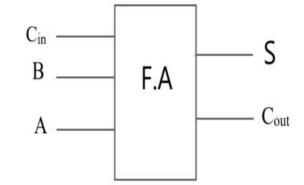

Full adder is difficult to implement than a half adder as it has three inputs. The first two inputs are A and B and the third input is an input carry as C-in. When full adder logic is designed, you string eight of them together to create a byte-wide adder and cascade the carry bit from one adder to the next. The output carry is designated as C OUT and the normal output is designated as S. The truth table of the full adder is listed in Table below:

| X | y | Z | C | S |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

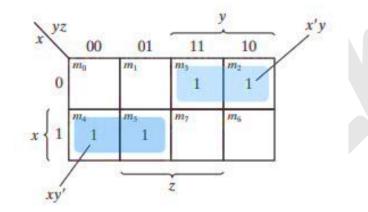

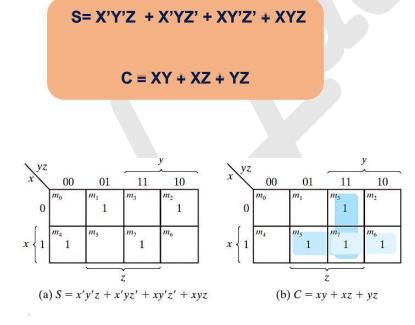

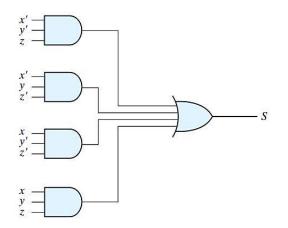

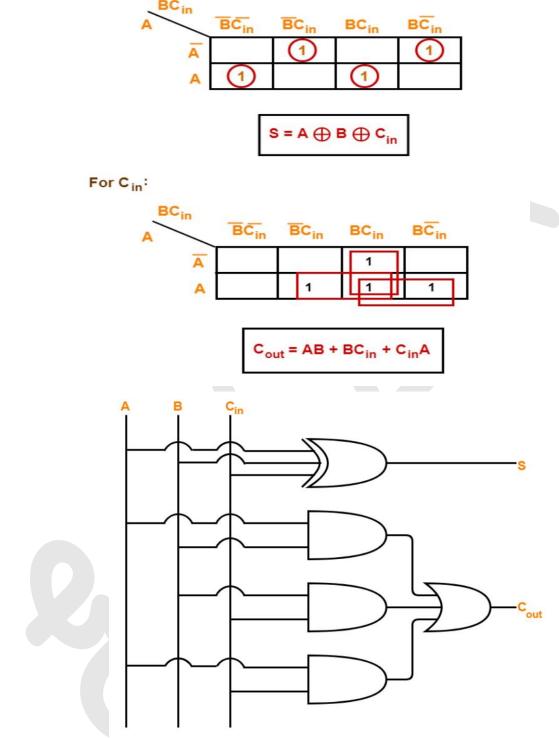

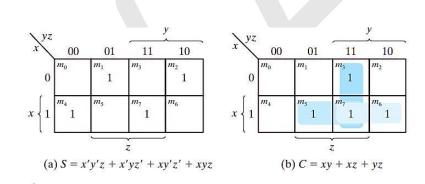

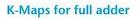

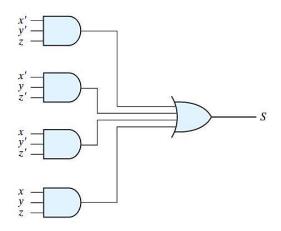

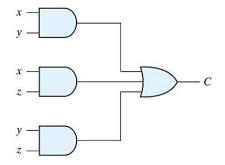

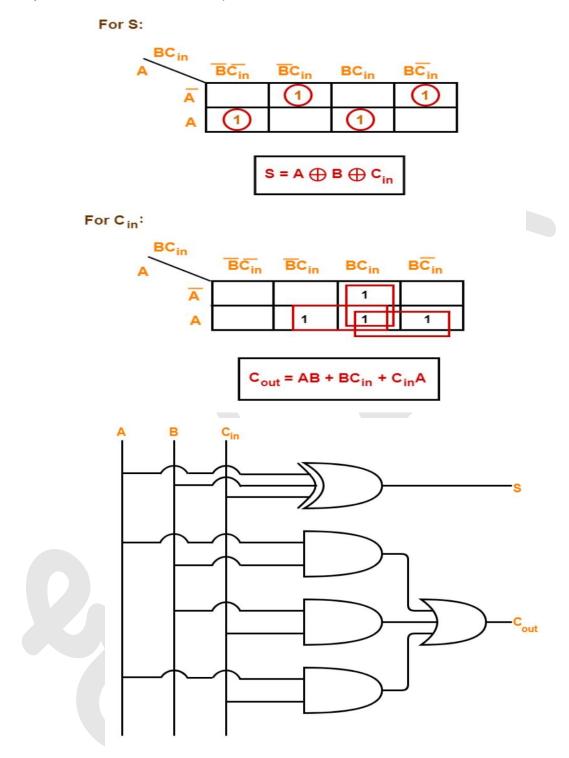

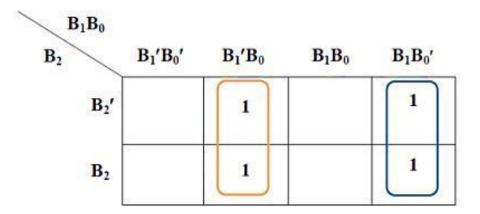

When all input bits are 0, the output is 0. The S output is equal to 1 when only one input is equal to 1 or when all three inputs are equal to 1. The C output has a carry of 1 if two or three inputs are equal to 1. The input and output bits of the combinational circuit have different interpretations at various stages of the problem. On the one hand, physically, the binary signals of the inputs are considered binary digits to be added arithmetically to form a two-digit sum at the output. On the other hand, the same binary values are considered as variables of Boolean functions when expressed in the truth table or when the circuit is implemented with logic gates. The maps for the outputs of the full adder are shown in Fig.2. As well as the logic diagram for the full adder implemented in sum-of-products form is shown in Fig. 2

While the simplified expressions are

For S: BCin

Full Adder Logic Diagram

Good luck Dena.N. Obed Agha Z

### **Digital Adder**

- In digital electronics an adder is a logic circuit that implements addition of numbers. In many computers and other types of processors, adders are used to calculate addresses, similar operations and table indices in the arithmetic logic unit (ALU) and also in other parts of the processors. These can be built for many numerical representations like binary coded decimal or excess-3.

- Adders are classified into two types:

- 1. Half adder

- 2. Full adder

Digital computers perform a variety of information-processing tasks. Among the functions encountered are the various arithmetic operations. The most basic arithmetic operation is the addition of two binary digits. This simple addition consists of four possible elementary operations:

✓ 0 + 0 = 0✓ 0 + 1 = 1✓ 1 + 0 = 1✓ 1 + 1 = 10

The first three operations produce a sum of one digit, but when both augend and addend bits are equal to 1, the binary sum consists of two digits. The higher significant bit of this result is called a **carry**. When the augend and addend numbers contain more significant digits, the carry obtained from the addition of two bits is added to the next higher order pair of significant bits. A combinational circuit that performs the addition of two bits is called a half adder. One that performs the addition of three bits (two significant bits and a previous carry) is a full adder. The names of the circuits stem from the fact that two half adders can be employed to implement a full adder.

# Half Adder

From the verbal explanation of a half adder, we find that this circuit needs two binary inputs and two binary outputs. The input variables designate the augend and addend bits; the output variables produce the sum and carry. We assign symbols x and y to the two inputs and S (for sum) and C (for carry) to the outputs. The truth table for the half adder is listed below. The C output is 1 only when both inputs are 1. The S output represents the least significant bit of the sum. The simplified Boolean functions for the two outputs can be obtained directly from the truth table.

#### **Communication Dept 1st Class**

#### **Electronics Engineering**

| X | y | C | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

The simplified sum-of-products expressions are

S = X'Y + XY' C= XY

The logic diagram of the half adder implemented in sum of products is shown in Fig. 1-(a). It can be also implemented with an exclusive-OR and an AND gate as shown in Fig. 1-(b). This form is used to show that two half adders can be used to construct a full adder.

2

# Full Adder

**Addition** of n-bit binary numbers requires the use of a full adder, and the process of addition proceeds on a bit-by-bit basis, right to left, beginning with the least significant bit. After the least significant bit, addition at each position adds not only the respective bits of the words, but must also consider a possible carry bit from addition at the previous position.

A full adder is a combinational circuit that forms the arithmetic sum of three bits. It consists of three inputs and two outputs. Two of the input variables, denoted by x and y, represent the two significant bits to be added. The third input, z or ( $C_{in}$ ), represents the carry from the previous lower significant position. *The output* carry is designated as  $C_{OUT}$  and the normal output is designated as **S**. The truth table of the full adder is listed in Table below:

| x | y | Z | C | S |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

When all input bits are 0, the output is 0. The S output is equal to 1 when only one input is equal to 1 or when all three inputs are equal to 1. The C output has a carry of 1 if two or three inputs are equal to 1. The input and output bits of the combinational circuit have different interpretations at various stages of the problem. On the one hand, physically, the binary signals of the inputs are considered binary digits to be added arithmetically to form a two-digit sum at the output. On the other hand, the same binary values are considered as variables of Boolean functions when expressed in the truth table or when the circuit is implemented with logic gates. The maps for the outputs of the full adder are shown in Fig.2. As well as the logic diagram for the full adder implemented in sum-of-products form is shown in Fig. 2

While the simplified expressions are

C = XY + XZ + YZ

Figure - 2

If you used A,B and  $C_{in}$  as inputs instead of X,Y and Z.

Full Adder Logic Diagram

Good luck Dena.N. Obed Agha Z

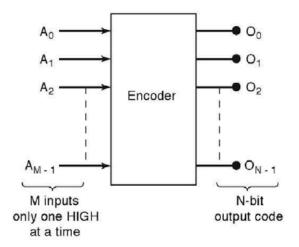

# **Encoder** and Decoder

### **Encoder:**

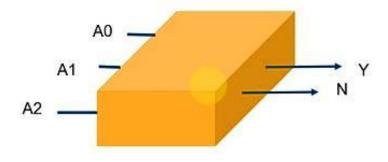

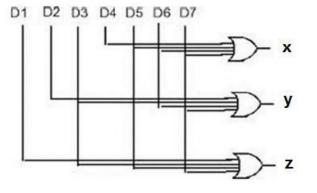

An encoder is a digital function that performs the inverse of a decoder. It has (2<sup>n</sup>) inputs and (n) outputs. The outputs lines generate the binary codes corresponding to the input values.

| D <sub>7</sub> | D <sub>6</sub> | Ds | D <sub>4</sub> | D3 | D <sub>2</sub> | D | D <sub>0</sub> | $A_2 A_1 A_0$ |

|----------------|----------------|----|----------------|----|----------------|---|----------------|---------------|

| 0              | 0              | 0  | 0              | 0  | 0              | 0 | 1              | 0 0 0         |

| 0              | 0              | 0  | 0              | 0  | 0              | 1 | 0              | 0 0 1         |

| 0              | 0              | 0  | 0              | 0  | 1              | 0 | 0              | 0 1 0         |

| 0              | 0              | 0  | 0              | 1  | 0              | 0 | 0              | 0 1 1         |

| 0              | 0              | 0  | 1              | 0  | 0              | 0 | 0              | 1 0 0         |

| 0              | 0              | 1  | 0              | 0  | 0              | 0 | 0              | 1 0 1         |

| 0              | 1              | 0  | 0              | 0  | 0              | 0 | 0              | 1 1 0         |

| 1              | 0              | 0  | 0              | 0  | 0              | 0 | 0              | 1 1 1         |

For this design it is assumed that only one input has a value of one at any given time.

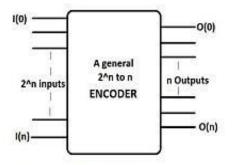

So A<sub>0</sub>=D<sub>1</sub>+D<sub>3</sub>+D<sub>5</sub>+D<sub>7</sub>

$A_1 = D_2 + D_3 + D_6 + D_7$

$$A_2 = D_4 + D_5 + D_6 + D_7$$

A General encoder's block diagram.

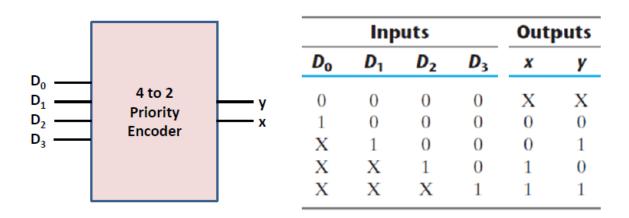

### **Priority Encoder:**

The operation of the priority encoder is such that if two or more inputs are equal to one at the same time, the input having the highest priority will take precedence.

| $D_3$ | $D_2$ | $D_1$ | $D_0$ | A <sub>1</sub> | A <sub>0</sub> | V |

|-------|-------|-------|-------|----------------|----------------|---|

| 0     | 0     | 0     | 0     | X              | Х              | 0 |

| 0     | 0     | 0     | 1     | 0              | 0              | 1 |

| 0     | 0     | 1     | Х     | 0              | 1              | 1 |

| 0     | 1     | X     | Х     | 1              | 0              | 1 |

| 1     | Х     | Х     | X     | 1              | 1              | 1 |

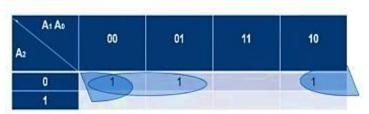

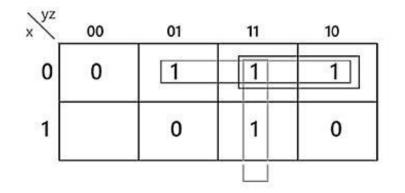

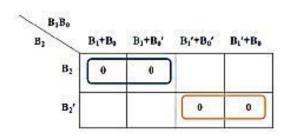

Thus:  $A_0 = D_3 | D_1 D_2'$

| 0,0,0 | 0 0 | 0 1 | 11 | 1 0 |

|-------|-----|-----|----|-----|

| 0.0   | d   | 0   | 1  | 1   |

| 0 1   | 0   | 0   | 0  | 0   |

| 1 1   | 1   | 1   | 1  | 1   |

| 1 0   | 1   | 1   | 1  | 1   |

And the same for A<sub>1</sub> and V:

$A_1 = D_2 + D_3$

$V - D_0 + D_1 + D_2 + D_3$

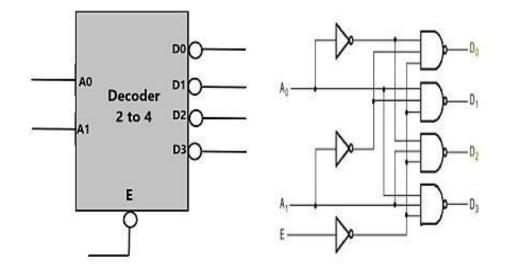

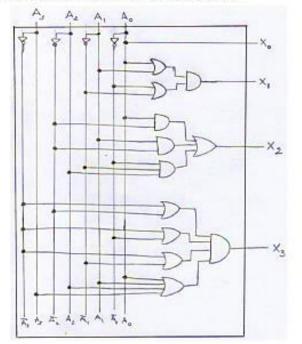

### Decoder:

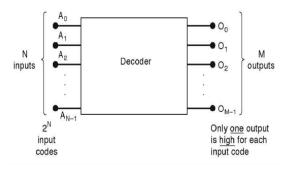

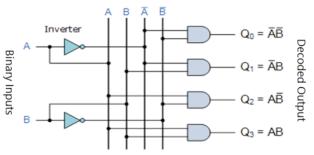

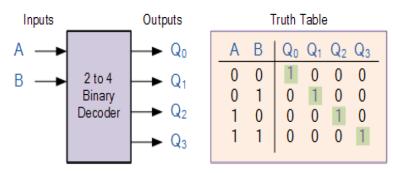

The decoder is a combinational circuit that converts binary information from (n) coded inputs to a maximum of  $(2^n)$  unique output.

| $A_2 A_1 A_0$ | D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> |

|---------------|-------------------------------------------------------------------------------------------------------------------------|

| 0 0 0         | 00000001                                                                                                                |

| 0 0 1         | 0 0 0 0 0 0 1 0                                                                                                         |

| 0 1 0         | 0 0 0 0 0 1 0 0                                                                                                         |

| 0 1 1         | 0 0 0 0 1 0 0 0                                                                                                         |

| 1 0 0         | 0 0 0 1 0 0 0 0                                                                                                         |

| 1 0 1         | 0 0 1 0 0 0 0 0                                                                                                         |

| 1 1 0         | 0 1 0 0 0 0 0 0                                                                                                         |

| 1 1 1         | 10000000                                                                                                                |

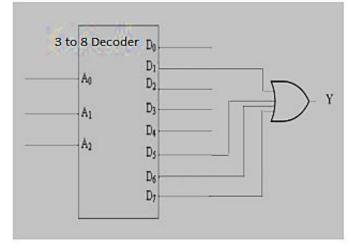

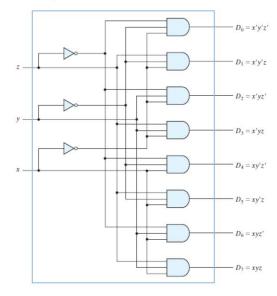

### 3 to 8 Decoder

D0=A2'A1'A0'

- D1=A2'A1'A0

- D3=A2'A1 A0

- D4=A2 A1'A0'

- D5=A2 A1'A0

- D6=A2 A1 A0'

$D_7 = A_2 A_1 A_0$

A General decoder's block diagram

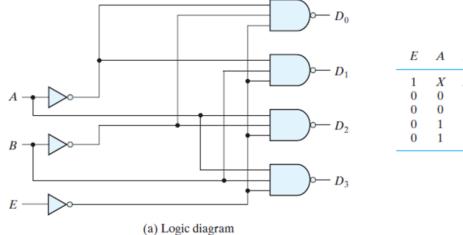

### **Decoder with Enable:**

### 3 to 8 Decoder with Enable

| E | A | A <sub>0</sub> | D3 | $D_2$ | $D_1$ | $D_0$ |

|---|---|----------------|----|-------|-------|-------|

| 0 | 0 | 0              | 1  | 1     | 1     | 0     |

| 0 | 0 | 1              | 1  | 1     | 0     | 1     |

| 0 | 1 | 0              | 1  | 0     | 1     | 1     |

| 0 | 1 | 1              | 0  | 1     | 1     | 1     |

| 1 | Х | Х              | 1  | 1     | 1     | 1     |

D0'=E'A1'A0'

D1'=E'A1'A0

$D_2' = E'A_1 A_0'$

D3'=E'A1 A0

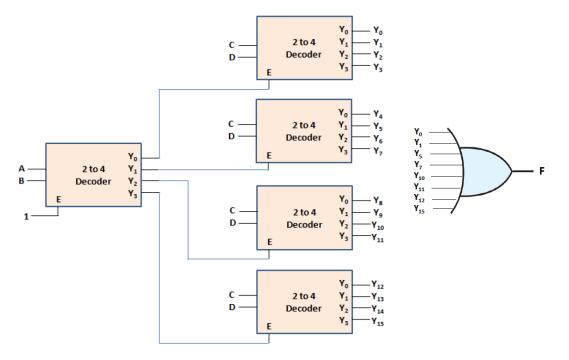

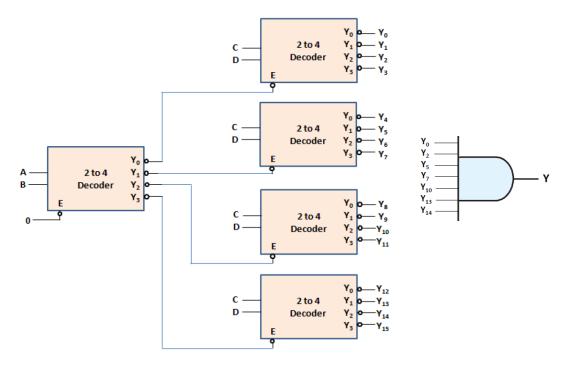

2 to 4 Decoder block diagram and internal logic circuit

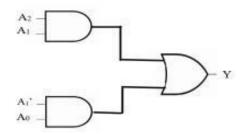

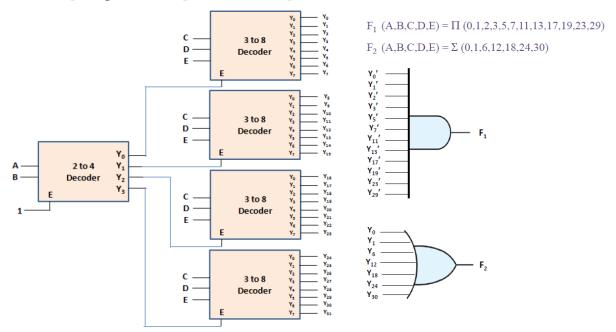

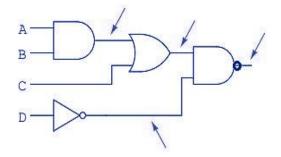

# **Decoder** applications

Example:

Find the output Y of the following canonical form:

$Y=\sum m(1,5,6,7)$

| $2^2 \ 2^1 \ 2^0$ |   |

|-------------------|---|

| A2 A1 A0          | y |

| 0 0 0             | 0 |

| 0 0 1             | 1 |

| 0 1 0             | 0 |

| 0 1 1             | 0 |

| 1 0 0             | 0 |

| 1 0 1             | 1 |

| 1 1 0             | 1 |

| 1 1 1             | 1 |

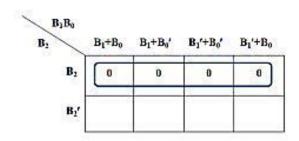

| A1A0 | 0 0 | 0 1 | 1 1 | 1 0          |

|------|-----|-----|-----|--------------|

| 0    | 0   |     | 0   | 0            |

| 1    | 0   |     |     | $\mathbf{D}$ |

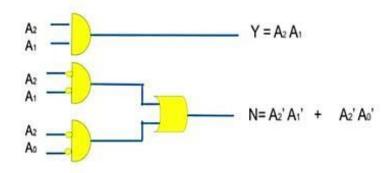

$Y = A_2A_1 + A_1'A_0$

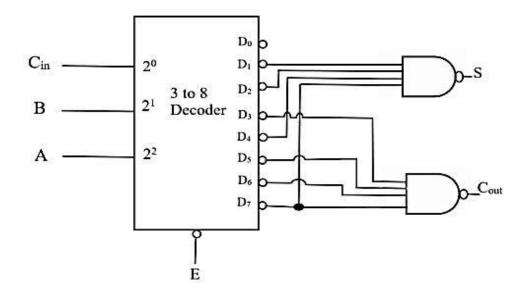

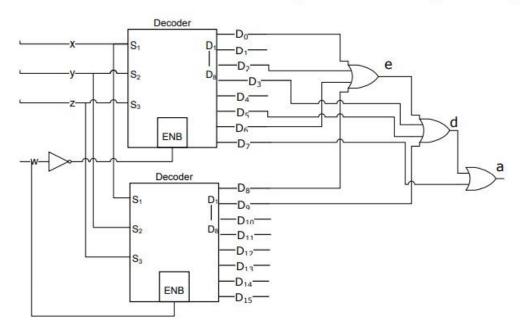

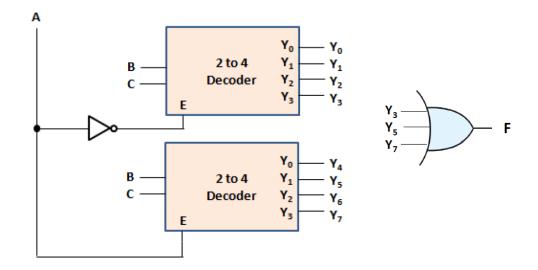

In order to solve the previous example by using a Decoder we need a 3 to 8 Decoder:

$Y = \sum m(1,5,6,7)$

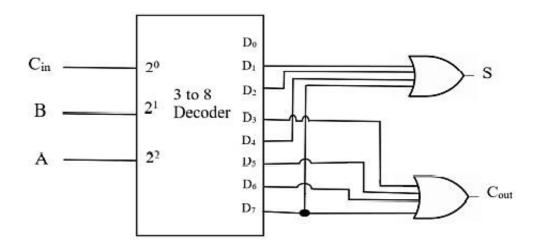

Full adder circuit using a Decoder:

| $2^2 2^1 2^0$       | 6.0000 ANO. |

|---------------------|-------------|

| A B C <sub>in</sub> | Cout S      |

| 0 0 0               | 0 0         |

| 0 0 1               | 0 1         |

| 0 1 0               | 0 1         |

| 0 1 1               | 1 0         |

| 1 0 0               | 0 1         |

| 1 0 1               | 1 0         |

| 1 1 0               | 1 0         |

| 1 1 1               | 1 1         |

#### **Communication Dept 1st Class**

### **Electronics Engineering**

DIGITAL TECHNIQUE

Design a F.A circuit using a Decoder with Enable:

| A B C <sub>in</sub> | Cout S |

|---------------------|--------|

| 0 0 0               | 0 0    |

| 0 0 1               | 0 1    |

| 0 1 0               | 0 1    |

| 0 1 1               | 1 0    |

| 1 0 0               | 0 1    |

| 1 0 1               | 1 0    |

| 1 1 0               | 1 0    |

| 1 1 1               | 1 1    |

Good luck Dena.N

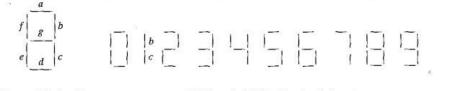

1

C

4

d

3

2

dp

5

e

1

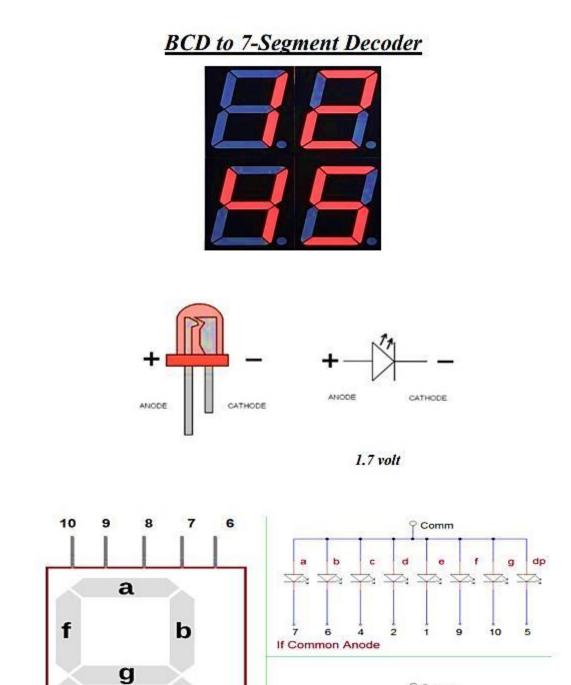

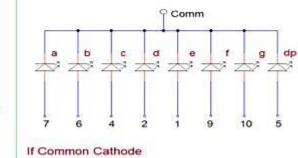

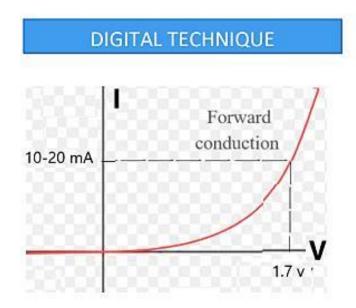

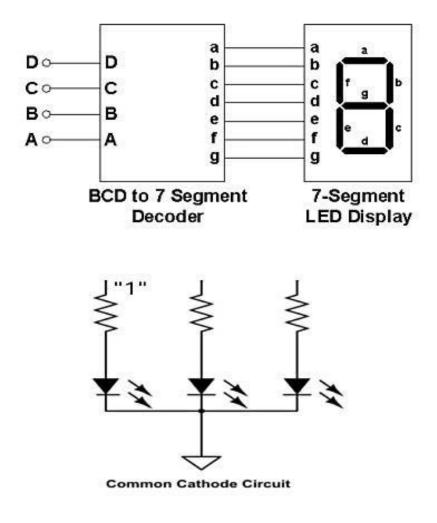

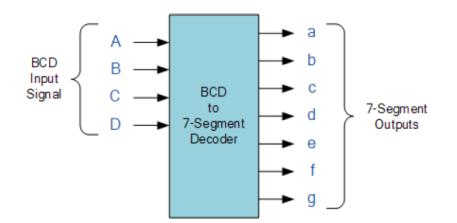

# BCD to 7-Segment Decoder common cathode

|                                                | ļ                | D-     | DI | GITAL  | TECH          | NIQU                  | JE.           |             |               |         |                  |

|------------------------------------------------|------------------|--------|----|--------|---------------|-----------------------|---------------|-------------|---------------|---------|------------------|

| 1                                              | 1                | B      | CD |        | 1             | De                    | ecod          | ed c        | outpu         | uts     |                  |

| Decimal                                        | Вз               | B2     | B1 | Во     | a             | b                     | с             | d           | е             | f       | g                |

| 0                                              | 0                | 0      | 0  | 0      | 1             | 1                     | 1             | 1           | 1             | 1       | 0                |

| 1                                              | 0                | 0      | 0  | 1      | 0             | 1                     | 1             | 0           | 0             | 0       |                  |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | 0<br>0           | 0      | 1  | 0      | 1             | 1                     | 0             | 1           | 1             | 0       | 0<br>1<br>1<br>1 |

| 3                                              | 0                | 0      | 1  | 1<br>0 |               | 1                     | 1             | 1           | 0             | 0       | 1                |

| 4                                              | 0                | 1      | 0  |        | 0             | 1                     | 1             | 0           | 0             | 1       | 1                |

| 5                                              | 0                | 1      | 0  | 1<br>0 | 1             | 0                     | 1             | 1           | 0             | 1       | 1                |

| 6                                              | 0                | 1      | 1  | 0      | 0             | 0                     | 1             | 1           | 1             | 1       | 1                |

| /                                              | 0                | 1<br>0 | 1  | 1      | 1             | 1                     | 1             | 0           | 0             | 0       | 0                |

| 8                                              | 1                | 0      | 0  | 0      | 1             | 1<br>1                | 1             | 1           | 1             | 1       | 1                |

| 9                                              | 0<br>1<br>1<br>1 | 0000   | 0  | 1      |               | 1                     | 1             | 0<br>X<br>X | v             | 1       | 1                |

|                                                | 1                | 0      | 1  | 0      | I Ŷ           | ××                    | Ŷ             | Ŷ           | Ŷ             | ×<br>×  | x<br>x           |

|                                                | 1                | 1      | 0  | o      | ÎŶ            | Ŷ                     | Ŷ             |             | Ŷ             | x       |                  |

|                                                | 1                | 1      | o  | 1      | Îx            | x                     | x             | x           | x             | x       | x                |

|                                                | 1                | 1      | 1  | 0      | x             | x                     | x             | x           | x             | x       | x                |

|                                                | 1<br>1<br>1      | 1      | 1  | 1      | X X X X X X X | X<br>X<br>X<br>X<br>X | × × × × × × × | X X X X     | 0 X X X X X X | X X X X | ××××             |

|                                                |                  | 47 F   | 80 | 00     | 01            | 11                    | 1             | 0           | /             | /       | × <sup>4</sup>   |

|                                                |                  | 00     |    | 1      | 0             | 1                     | 1             |             | <u></u>       |         |                  |

|                                                |                  | 01     |    | 0      | 1             | 1                     | 1             |             |               |         |                  |

|                                                |                  | 11     |    | x      | x             | x                     | ×             | 7           |               |         |                  |

|                                                |                  | 10     | Į  | 1      | 1             | x                     | ×             |             | /             |         |                  |

| 1                                              | /                | /      | 3  | /      |               |                       |               |             |               |         | 2                |

3

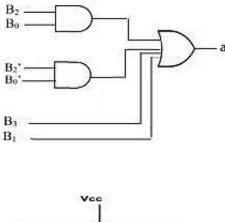

### DIGITAL TECHNIQUE

$a = B_3 + B_1 + B_2 B_0 + B_2 B_0'$

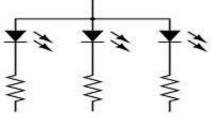

Common Anode Circuit

# Scale of Integration:

The number of components fitted into a standard size IC represents its integration scale, in other words it is a density of components. It is classified as follows:

- 1. SSI- Small Scale Integration (less than 10 gates)

- 2. MSI- Medium Scale Integration (10-100 gates)

- 3. LSI- Large Scale Integration (100-3000 gates)

- 4. VLSI- Very Large Scale Integration (≈ millions)

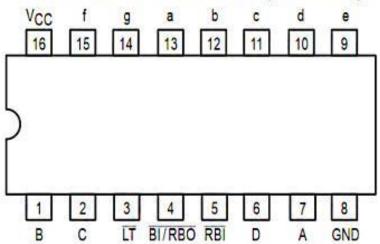

# **BCD TO 7-SEGMENT DECODER**

### CONNECTION DIAGRAM DIP (TOP VIEW)

#### PIN NAMES